本篇目录:

- 1、常用逻辑电平标准总结

- 2、lvttl是什么

- 3、低压差分信号?

- 4、电路中什么是高电平低电平?

- 5、LVDS电平的使用注意

- 6、LVDS电平的LVDS的应用模式

常用逻辑电平标准总结

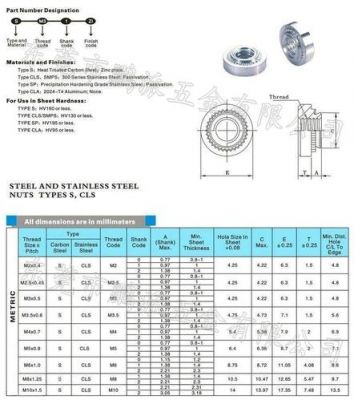

和上面的GTL相似,输入为输入为比较器结构,比较器一端接参考电平(VCCIO/2),另一端接输入信号。对参考电平要求比较高(1%精度)。

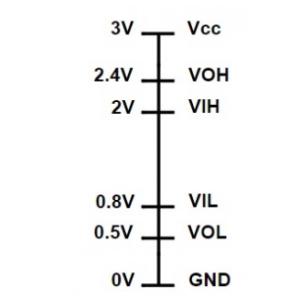

:输入高电平(Vih): 保证逻辑门的输入为高电平时所允许的最小输入高电平,当输入电平高于Vih时,则认为输入电平为高电平。

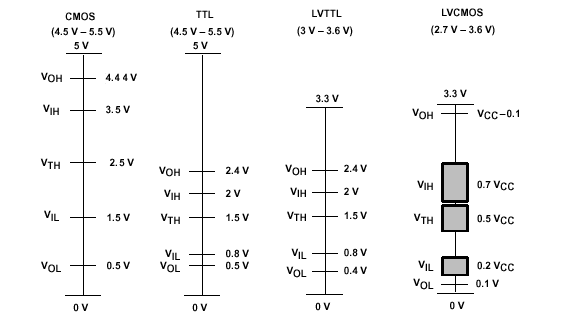

现在常用的是:TTL数字电路电源是5V,7V 高电平 5V, 0V (=) 低电平 3V。CMOS数字电路电源电压一般是3V--9V, 2/3VCC 高电平 (=) VCC,0V (=) 低电平1/3VCC。

·RS-422/485和RS-232是串口的接口标准,RS-422/485是差分输入输出,RS-232是单端输入输出。一点补充:RS-232C采用的是负逻辑,即逻辑“1”:-5V至-15V; 逻辑“0”:+5V至+15V。

LS系列集成电路采用(TTL)逻辑电平标准,74HC系列集成电路采用(CMOS)逻辑电平标准。

lvttl是什么

LvTTL接口是一种数字电平标准,是一种标准逻辑器件输入或输出的电平标准,其中Lv代表电平,TTL即Transistor-Transistor Logic,是指采用晶体管作为开关元件的数字电路逻辑。

第5个X,如为1代表LVTTL。如为16位和32位的芯片,第5个X已被占用,则第5个X有双重含义,如1代表2个Bank和LVTTL,3代表4个Bank和LVTTL。 G5为TSOPII封装。

对改善噪声容限没好处,会增大系统功耗,并影响速度,所以后来出现LVTTL(Low Voltage TTL)。在晶振产品中,LVTTL分为3V、5V,其中以3V为主。

低压差分信号?

LVDS即低压差分信号传输 是一种满足当今高性能数据传输应用的新型技术。由于其可使系统供电电压低至2V,因此它还能满足未来应用的需要。此技术基于ANSI/TIA/EIA-644LVDS接口标准。

LVDS代表低压差分信号(Low-Voltage Differential Signaling),是一种数字信号传输技术。LVDS线是用于传输LVDS信号的电缆或线缆。

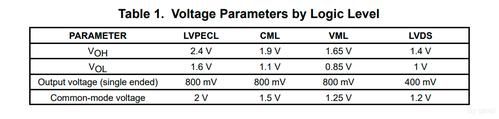

LVDS:Low Voltage Differential Signaling,低电压差分信号。LVDS传输支持速率一般在155Mbps(大约为77MHZ)以上。

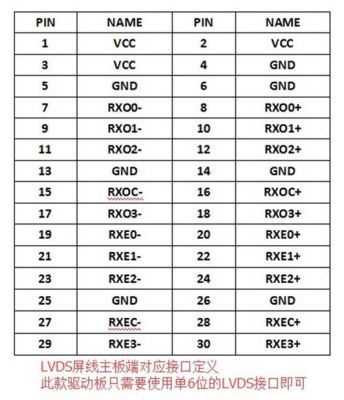

LVDS是低压差分信号(LOW VOLTAGE DIFFERENGIAL SIGNAL),由于低电压和良好信号、屏蔽效果主要用于屏幕和主板上的连接,较多的用于液晶显示器、液晶电视、笔记本电脑中。希望能帮到你。

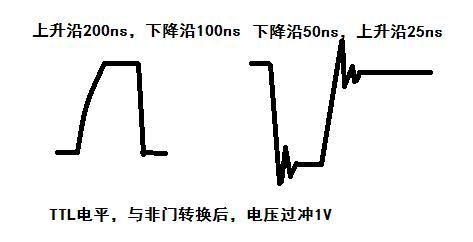

ANSI/TIA/EIA-644中,推荐最大速率为655Mbps,理论极限速率为923Mbps。 LVDS信号传输一般由三部分组成:差分信号发送器,差分信号互联器,差分信号接收器。差分信号发送器:将非平衡传输的TTL信号转换成平衡传输的LVDS信号。

电路中什么是高电平低电平?

高电平,指的是与低电平相对的高电压,是电工程上的一种说法。在逻辑电平中,保证逻辑门的输入为高电平时所允许的最小输入高电平,当输入电平高于输入高电压(Vih)时,则认为输入电平为高电平。

高电平(High Level):通常指逻辑1,其电压范围为4V至5V之间。一般情况下,接近5V的电压被视为高电平。低电平(Low Level):通常指逻辑0,其电压范围为0V至0.8V之间。一般情况下,接近0V的电压被视为低电平。

高电平和低电平都是电力工程当中的一种。高电平是指在逻辑电平中,保证逻辑门的输入为高电平时所允许的最小输入高电平,如果输入的电平高于输入高电压(Vih),这个时候我们就说这个电平是高电平。

LVDS电平的使用注意

1、LVDS是点到点应用通信标准。 多点LVDS (M-LVDS)则是一种面向多点应用的类似标准。 两种技术在实际工程应用中都需要注意以下几点,以得到更好的使用体验。

2、③ 具有相对较慢的边缘速率(dV/dt约为0.300 V/0.3 ns,即为1 V/ns),同时采用差分传输形式,使其信号噪声和EMI都大为减少,同时也具有较强的抗干扰能力。所以,LVDS具有高速、超低功耗、低噪声和低成本的优良特性。

3、LVDS是液晶屏的信号模式,是数字类型的,不是模拟的,2ch,8-bit就是通常所说的双8位屏线接口,所接的屏线就只能用双8位的。

4、lvds电池保护功能:当电池的电量是从100%的电量下降到95%-100%之间的时候,再插入电源的时候,电源是不对电池进行充电的。这时候的机器并不是不能对电池充电,而是处于过充电保护,系统使用交流电源进行供电。

5、LVDS:Low Voltage Differential Signaling 差分对输入输出,内部有一个恒流源5-4mA,在差分线上改变方向来表示0和1。通过外部的100欧匹配电阻(并在差分线上靠近接收端)转换为±350mV的差分电平。

6、LVDS是英文Low.Voltage.Differential.Signaling的缩写,是一种低压差分信号接口技术,它是美国国家半导体(NS)公司为克服以TTL电平方式传输宽带高码率数据时功耗大、电磁干扰大等缺点而研制的一种数字视频信号传输方式。

LVDS电平的LVDS的应用模式

LVDS即低电压差分信号,这种技术的核心是采用极低的电压摆幅高速差动传输数据,具有低功耗、低误码率、低串扰和低辐射等特点,其传输介质可以是铜质的PCB连线,也可以是平衡电缆。

最基本的LVDS器件就是LVDS驱动器和接收器。LVDS的驱动器由驱动差分线对的电流源组成,电流通常为5 mA。

相较而言,M-LVDS驱动器强度更高,在负载为 50 Ω(两个100 Ω的端接电阻,总线的任意一端)的情况下,最小输出电压摆幅|VOD|为480 mV,最大值则为650mV,所以可以解决多点应用中的问题。

LVDS:Low-Voltage Differential Signaling 低压差分信号 1994年由美国国家半导体公司提出的一种信号传输模式,是一种电平标准,广泛应用于液晶屏接口。

LVDS是液晶屏的信号模式,是数字类型的,不是模拟的。2ch,8-bit 就是通常所说的双8位屏线接口,所接的屏线就只能用双8位的。LVDS,即Low Voltage Differential Signaling,是一种低压差分信号技术接口。

LVDS使用注意:可以达到600MHz以上,PCB要求较高,差分线要求严格等长,差最好不超过10mil(0.25mm)。100欧电阻离接收端距离不能超过500mil,最好控制在300mil以内。

到此,以上就是小编对于lvds 电平标准的问题就介绍到这了,希望介绍的几点解答对大家有用,有任何问题和不懂的,欢迎各位老师在评论区讨论,给我留言。

微信扫一扫打赏

微信扫一扫打赏