本篇目录:

RTL级代码和仿真代码的区别

RTL级行为仿真(又称作为功能仿真、前仿真);综合后门级仿真;时序仿真(又称为后仿真)。第一个仿真可以用来检查代码中的错误以及代码行为的正确性,其中不包括信息。

RTL级是比门级更高的抽象层次,使用RTL级语言描述硬件电路一般比门级描述简单高效得多。RTL级语言的最重要的特性是:RTL级描述是可综合的描述层次。

RTL级和门级简单的区别在于,RTL是用硬件描述语言(Verilog 或VHDL)描述理想达到的功能,门级则是用具体的逻辑单元(依赖厂家的库)来实现你的功能,门级最终可以在半导体厂加工成实际的硬件。

也可以叫 RTL级仿真 和 Gate-level仿真也可以叫 功能仿真(RTL)、综合后仿真(post-synthesis)和布局布线仿真(Gate-level)。 其实,就看你从哪里划分了。 很多资料中更多的是看到 前仿真和后仿真。

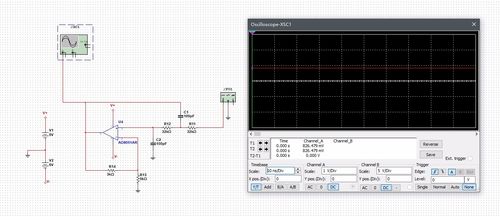

前仿真,也称为RTL级仿真或功能仿真。通过HDL仿真器验证电路逻辑功能是否有效,在前仿真时,通常与具体的电路实现无关,没有时序信息。逻辑综合。

RTL代码仿真:直接对verilog或者VHDL语言进行加入激励仿真。门级电路仿真:将代码转换成门级网表加入激励仿真。

怎么看quartusII中自带元件的源代码

准备好HDL源文件,编译综合都能通过,在project navigator 中的file 目录下找到源文件,右键点击源文件,选中 create symbol files for current file;完成后就生成了原理图,不过符号只能在符号文件中打开使用。

如图,在原理图输入界面双击,再出现的Symbol对话框中左侧选择。

要使用QuartusII 进行仿真,首先进行代码编译。代码输入完成后,点击start compilation按钮开始编译,编译完毕后,点击新建按钮,新建一个WaveForm文件。

双击打开QuartusII软件,选择 file---New Project Wizard...弹出如下窗口,本窗口介绍创建一个工程需要执行的设置,点击next。

打开quartus II,用verilog源文件,先点击file文件,下来菜单点击create/update。然后我们选择右侧的create symbol file for current file生成原理图。打开后界面随意右键弹出下来列表,选择insert。

先将驱动代码bq27501文件夹复制到 ti-davinci/drivers/ 目录下。确定bq27501驱动模块应在内核源代码树中处于何处。

verilog如何写寄存器读入读出

首先要DA芯片提供读写寄存器的接口,然后需要知道此接口的协议是什么。然后用verilog来实现此协议的接口,就可以读写数据了。

从高位读还是从低位读?10个字节80bit。

数字中不定值x或X,高阻值z或Z,和在下划线(_)的使用方法及代表的意义与一般Verilog HDL程序中的用法和意义是一样的。另外,数字必须用空白位置或注释行来分隔开。

rtl代码是前端还是后端

在后端设计流程中将feedthrough逻辑加入到RTL(Register Transfer Level)中通常有以下几个步骤: RTL设计:首先,你需要完成RTL设计,这包括使用硬件描述语言(如Verilog或VHDL)编写逻辑代码,定义各个模块的功能和互联关系。

FPGA (Field-Programmable Gate Array)属于前端。原因是FPGA是一种可编程逻辑设备,它提供了一种用于实现数字电路的可编程硬件平台。在设计FPGA时,需要进行逻辑综合、布局布线和时序优化等前端设计工作。

根据个人掌握的知识,写写自己的理解。前端设计(也称逻辑设计)和后端设计(也称物理设计)并没有统一严格的界限,涉及到与工艺有关的设计就是后端设计。

到此,以上就是小编对于rtl级代码的问题就介绍到这了,希望介绍的几点解答对大家有用,有任何问题和不懂的,欢迎各位老师在评论区讨论,给我留言。

微信扫一扫打赏

微信扫一扫打赏