本篇目录:

cmos门电路怎么判断输出状态

而cmos逻辑门电路输入端不管是接大电阻还是接小电阻该端都相当于低电平即地电位。

两图中,下拉电阻值均<<1MΩ,与之相连的输入端电平为0,输出状态就很好判断了。

输出状态就是指输出的是高电平,还是低电平。

第一个是或非门,其逻辑功能可概括为“有1出0,全0出1”。现在有一个输入通过10kΩ接地,相当于高电平1,所以输出应该是低电平0。第二个是与非门,逻辑功能为“有0出1,全1出0”。

a)Y=1,10K电阻接地相当于输入0,与非门见0出1。b)Y=0,或非门输入有1,(0+1)`=0。c)Y=0,或非门上面一个与门输入为1,(0+1)`=0。d)Y=0,两与非门线与,0与1=0。

(C)对于CMOS逻辑电路,因其输入电阻极大,上、下拉电阻的限值为≤1MΩ。

怎么判断ttl门电路的输出状态

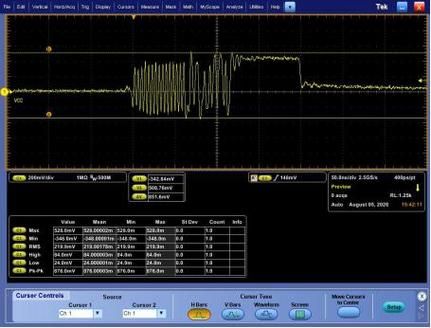

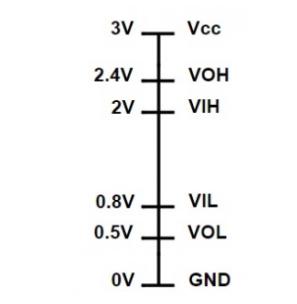

1、Vcc为逻辑高电平,悬空近似为逻辑高电平。Vih为输入高电平,ViL为输入低电平。通过各种与非门,或非门、与或非门等等的逻辑运算就可判断出电路的输出状态。

2、当某输入端悬空,TTL电路视这输入为1,EN为使能输入,高电平有效,有小圈就低电平有效,输出有倒三角为集电极开路输出类型。

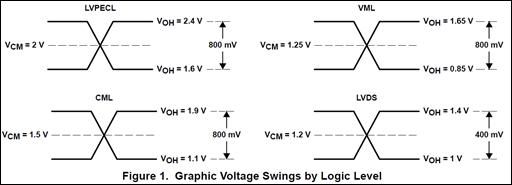

3、(一)TTL高电平6~5V,低电平0V~4V CMOS电平Vcc可达到12V CMOS电路输出高电平约为0.9Vcc,而输出低电平约为 0.1Vcc。 CMOS电路不使用的输入端不能悬空,会造成逻辑混乱。

4、输入端接电源,悬空或高阻(10k以上)相当于接高电平,接地为低电平,通过低阻接入电平信号则认为输入信号与接入电平相同。

5、ttl输入端为低电平时,输出就会是高阻态。TTL具有高电平、低电平和高阻态三种输出状态。ttl功能如下:限制IP数据包在计算机网络中的存在的时间。避免IP包在网络中的无限循环和收发,节省了网络资源。

6、TTL的内部等效电路如下:因此输入如果悬空,相当于输入高电平;10欧姆电阻接地,接近于对地短路,相当于输入低电平。

逻辑门的输出是什么?

个逻辑门电路有三种输出,即高电平输出(正逻辑1或负逻辑0)、低电平输出(正逻辑0或负逻辑1)、高阻态输出。在数字电路中,所谓门就是只能实现基本逻辑关系的电路。

是的。第一个是或非门,其逻辑功能可概括为“有1出0,全0出1”。现在有一个输入通过10kΩ接地,相当于高电平1,所以输出应该是低电平0。第二个是与非门,逻辑功能为“有0出1,全1出0”。

高电平,有关。低电平。输入端接电源,悬空或高阻(10k以上)相当于接高电平,接地为低电平,通过低阻接入电平信号则认为输入信号与接入电平相同。则为OC门。

门电路逻辑功能及测试实验原理

1、常规门电路,输出依输入出0或1。OC门电路,原理为:集电极开路,使用时要外接上拉电阻,可用于线与。三态门电路,原理为:设有选中控制端端,没被选中的话输出高阻态,相当于未接入线路,用于总线数据传送。

2、实验原理:当输入端为电平高(+5V)时,输出端电平为电平低(0V);当输入端为电平低0V时,输出端电平为电平高(+5V),即,输入输出电平相反。NOT门是一种逻辑反演器,其实现的是逻辑非运算。

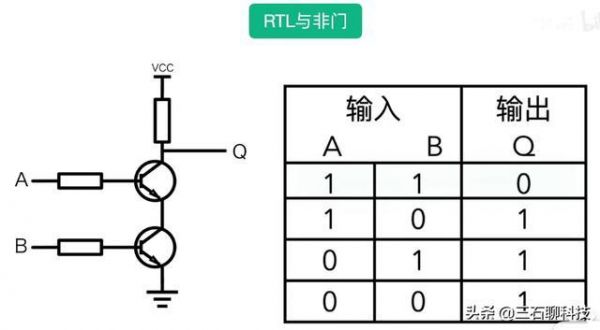

3、根据表达式可以得知其工作原理:先对A和B输入变量进行与运算得到结果x,再将得到的结果x进行取反,最终结果为x的反变量,得到输出结果Y。

到此,以上就是小编对于逻辑门怎么检测输出电压的问题就介绍到这了,希望介绍的几点解答对大家有用,有任何问题和不懂的,欢迎各位老师在评论区讨论,给我留言。

微信扫一扫打赏

微信扫一扫打赏