本篇目录:

- 1、xilinx的bit文件格式如何写入FPGA

- 2、fpga如何在bit流中增加版本信息

- 3、fpga开发流程

- 4、如何从零设计一颗简单的FPGA芯片?

- 5、Vivado安装、生成bit文件及烧录FPGA的简要流程

- 6、fpga生成的bit文件如何设置时间

xilinx的bit文件格式如何写入FPGA

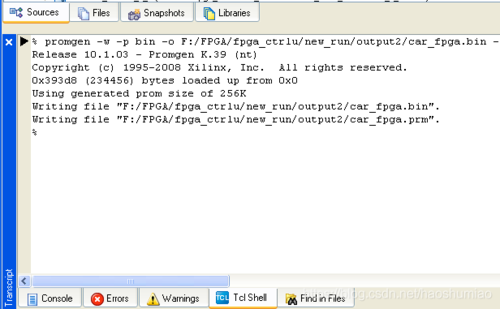

1、当你想把bit文件通过程序写入fpga的时候,你会发现总是不对。因为bit式是bitgen生成的jtag用的式。使用impact工具能够完成转换。

2、FPGA 生成的bit文件,就是一个Hex文件,你只需要按照器件推荐的时序要求写入FPGA即可。这部分的详细说明见使用器件配置说明哪个章节。

3、需求分析和规划 在开始FPGA开发之前,首先需要明确应用场景和需求,例如数据加速、信号处理、图像处理等。根据需求,进行系统架构规划和算法设计。

4、使用Vivado制作FPGA的简要流程在Windows下安装XilinxVivadoDesignSuite:XilinxVivadoDesignSuite安装文件,解压后得到安装目录:运行xsetup.exe文件,进入安装程序。如果提示要更新就直接点continue关掉。

5、这个很简单。这个是Xilinx公司的产品,下载程序有两种,一种是BIT文件那是下载到FPGA中的,一种一般是MCS文件,一般下载到EEPROM中。至于你所说的EEPROM还是RAM,下载到FPGA内的是存在RAM中的,下载到配置器件中的是EEPROM。

6、IBERT在CORE generator里产生工程和BIT文件。将BIT文件下载到FPGA后,使用ChipScope Analyzer连接到FPGA上,就会出现IBERT的GUI调试界面。 a) 检查PLL是否LOCK,如果没有,需要检查时钟和电源。

fpga如何在bit流中增加版本信息

当FPGA启动时,加载控制器会从地址0开始读取加载指令。当读到WBSTAR和IPROG指令时,控制器就跳转到WBSTAR指定的地址读取新的加载指令。在第二个配置文件中不再发IPROG指令,控制其将顺序执行以直到配置文件结束。

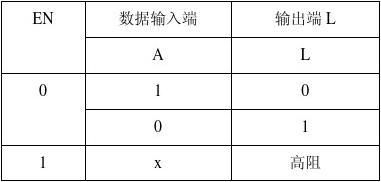

ProASIC3内部具有1kbit的Flash ROM可供用户使用,类似于普通的ROM操作,通过上位机软件将数据固化在FPGA内部的FROM,FPGA在运行的过程中只能进行读操作,可以用于存放密钥、序列号、版本号等信息。

FPGA 生成的bit文件,就是一个Hex文件,你只需要按照器件推荐的时序要求写入FPGA即可。这部分的详细说明见使用器件配置说明哪个章节。

fpga开发流程

1、通常可将FPGA/CPLD设计流程归纳为以下7个步骤,这与ASIC设计有相似之处。设计输入。Verilog或VHDL编写代码。前仿真(功能仿真)。设计的电路必须在布局布线前验证电路功能是否有效。

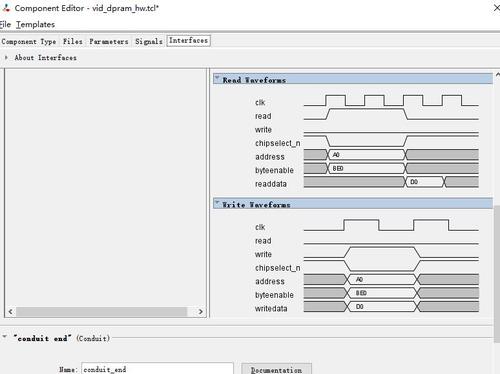

2、设计输入 设计输入是将所设计的系统或电路以开发软件要求的某种形式表示出来,并输入给EDA工具的过程。常用的方法有硬件描述语言(HDL)和原理图输入方法等。

3、FPGA 的设计开发流程主要包括四个步骤:设计输入(Design Entry)、仿真(Simulation)、综合(Synthesis)及布局布线(Place & Route)。

4、设计的最后一步就是芯片编程与调试。芯片编程是指产生使用的数据文件(位数据流文件,Bitstream Generation),然后将编程数据下载到FPGA芯片中。其中,芯片编程需要满足一定的条件,如编程电压、编程时序和编程算法等方面。

5、前面说了点废话,具体fpga的开发流程我列一下,纯属个人意见,参考一下吧 分析需求,根据需求出方案 方案定后,如果需要fpga,就要考虑io需求。

6、FPGA开发一般流程是:LOGIC-调试-综合-管脚分配,时序约束等-生成BIT文件-下载。IC一般流程是:CODE-前仿真验证-综合-综合后仿真-版图-后仿真-流片。

如何从零设计一颗简单的FPGA芯片?

1、剩下就要看你从事的硬件设计是什么方向了,比如cpu设计、多媒体、音视频压缩、通讯等,很多方面。首先还是把学校教的课学扎实吧,别看很多课现在没什么用,等到你真的要用的时候,如果有底子还是很好的。

2、验证。得保证电路功能的正确性,也叫验证,可以通过软件仿真,硬件仿真等方式实现。软件仿真一般比较直观,方便调试,因为每一时刻的状态都可以看到,这好比调试软件程序。

3、电路功能设计 在系统设计之前,首先要进行的是方案论证、系统设计和FPGA芯片选择等准备工作。

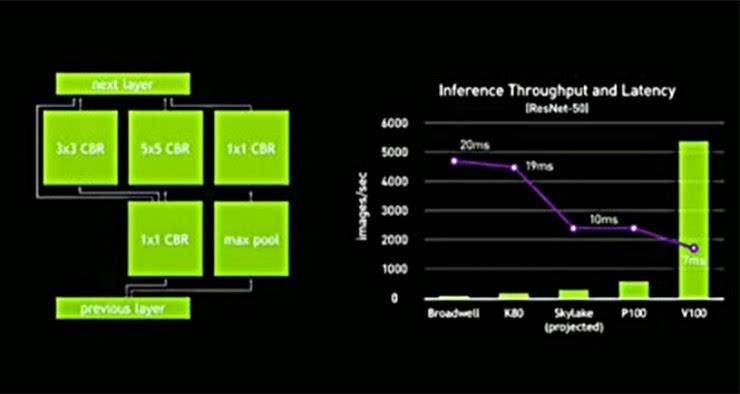

4、需求分析和规划 在开始FPGA开发之前,首先需要明确应用场景和需求,例如数据加速、信号处理、图像处理等。根据需求,进行系统架构规划和算法设计。

5、芯片编程与调试 设计的最后一步就是芯片编程与调试。芯片编程是指产生使用的数据文件(位数据流文件,Bitstream Generation),然后将编程数据下载到FPGA芯片中。

6、通常可将FPGA/CPLD设计流程归纳为以下7个步骤,这与ASIC设计有相似之处。设计输入。Verilog或VHDL编写代码。前仿真(功能仿真)。设计的电路必须在布局布线前验证电路功能是否有效。

Vivado安装、生成bit文件及烧录FPGA的简要流程

首先下载vivado webpack installer,目前最新版本为2011。开始安装,可以选择VIvado HL Webpack版本点击next继续安装。接下来的一步可以使用默认选项继续安装,但是这样占用的存储空间比较大。也可以使用如用所示的最小安装方式。

首先要去下载vivado的安装包。建议去官网下载下载好了安装解压。这个时间有点长。安装好了就打开,打开之后会出现三个问题,三个全选I Agree,然后点击NEXT。

)点击 bitstream setting ,将 bin_file 勾上,点击 OK。2)点击 generate bitstream ,生成 bit 文件和 bin 文件 3)点击 open hardware manager,连接板子。4)选中芯片,右键如下操作。

确定需求:首先,需要确定FPGA芯片需要实现什么功能。这将有助于确定芯片的规格,包括芯片大小、输入/输出接口和逻辑资源数量等。选择开发工具:选择一种FPGA开发工具,例如Xilinx Vivado或Altera Quartus,以便开始设计。

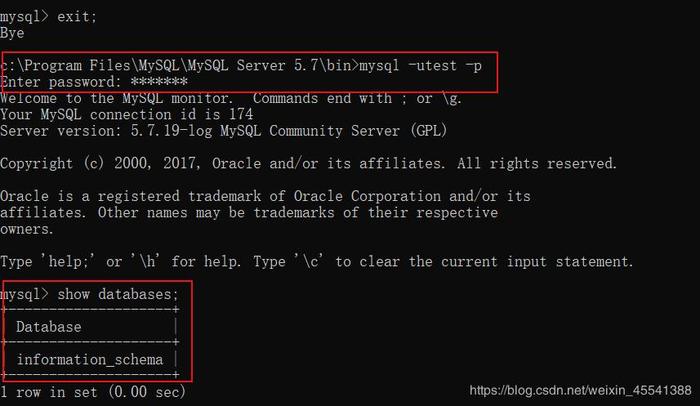

再下一步,这样ILA的设置工作就完成了。可以在debug视图中看到,Vivado自动帮我们插入了dbg_bug和ila,接下来生成bit文件,写入FPGA中,在Vivado的调试界面上就能进行在线的波形输出了。

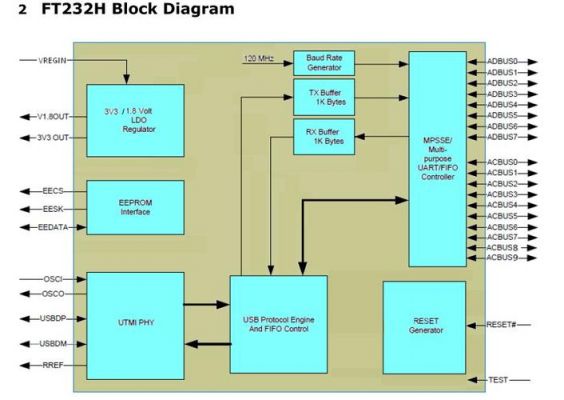

生成bit文件。使用bit文件生成mcs文件,生成的mcs文件时的flash参数要与实际使用的flash参数一致。JTAG线连到板子上,打开hardware manager,识别出器件。鼠标点击扫描出的器件,右键点击器件,选择add configuration memory device。

fpga生成的bit文件如何设置时间

FPGA获取bit生成时间,需要考虑到以下因素:设计复杂度:FPGA设计复杂度越高,需要生成的bit文件越多,生成时间也会相应增加。

首先,在ISE上运行,测试开始时间是7:33:10,生成bit文件的时间是7:37:01,共花了231秒。然后,在Vivado上运行。

生成的bit文件,就是一个Hex文件,你只需要按照器件推荐的时序要求写入FPGA即可。这部分的详细说明见使用器件配置说明哪个章节。

到此,以上就是小编对于fpga怎么配置通信设备的问题就介绍到这了,希望介绍的几点解答对大家有用,有任何问题和不懂的,欢迎各位老师在评论区讨论,给我留言。

微信扫一扫打赏

微信扫一扫打赏