本篇目录:

- 1、...8先译码器74LS138和基本逻辑电路构成一位全加器电路,画出电路连线...

- 2、用两个74hc151数据选择器实现全加器的实验

- 3、4位加法器能否作为3位加法器用?与输入的3位二进制数如何连接?共有多少...

...8先译码器74LS138和基本逻辑电路构成一位全加器电路,画出电路连线...

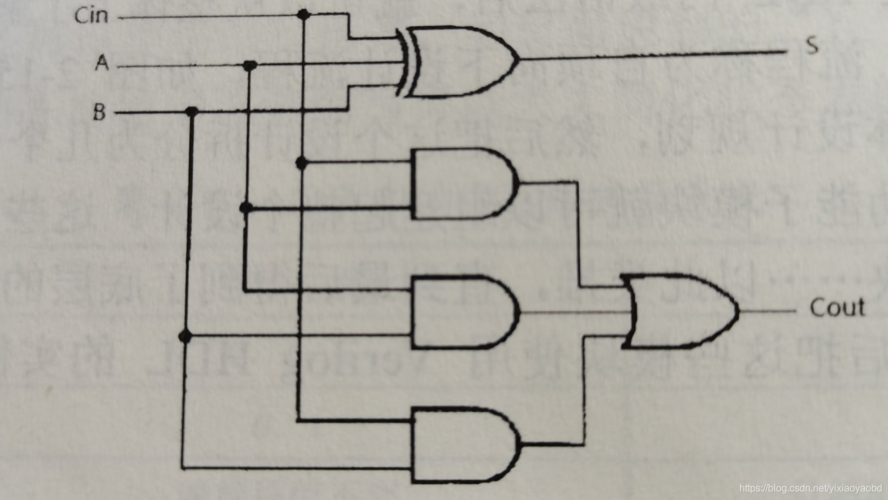

首先得弄清楚全加器的原理,你这里说的应该是设计1位的全加器。全加器有3个输入端:a,b,ci;有2个输出端:s,co.与3-8译码器比较,3-8译码器有3个数据输入端:A,B,C;3个使能端;8个输出端,OUT(0-7)。

一位全加器可以处理低位进位,并输出本位加法进位。多个一位全加器进行级联可以得到多位全加器。常用二进制四位全加器74LS283。

组合逻辑电路的分析分以下几个步骤:(1)有给定的逻辑电路图,写出输出端的逻辑表达式;(2)列出真值表;(3)通过真值表概括出逻辑功能,看原电路是不是最理想,若不是,则对其进行改进。

b=0,ci=1时。对应3-8译码器的输入为A=1,B=0,C=1,这是译码器对应的输出为OUT(5)=1,其余的为0,根据上面设计的连接关系,s=0,co=1,满足全加器的功能,举其他的例子也一样,所以,设计全加器的设计正确。

令74LS138的三个选通输入依次是ABC。Y1=AC的话 列出真值表,当ABC=101或者111的时候 Y1=1。 当ABC=101时,译码器选择Y5(即此时Y5输出0,其余输出1) 将Y5和Y7接到门电路的与非门即可。

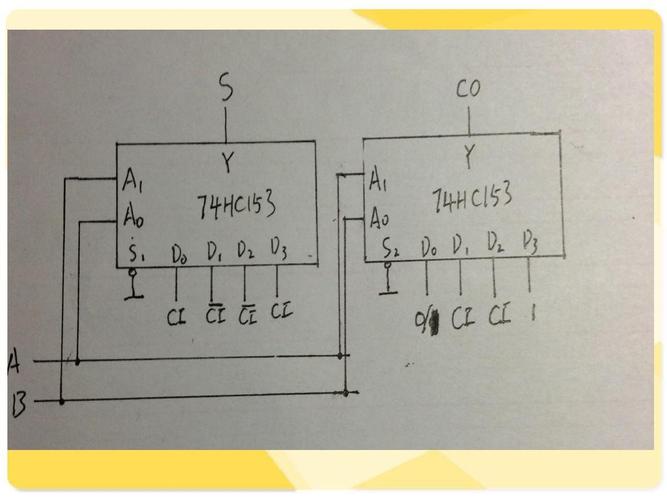

用两个74hc151数据选择器实现全加器的实验

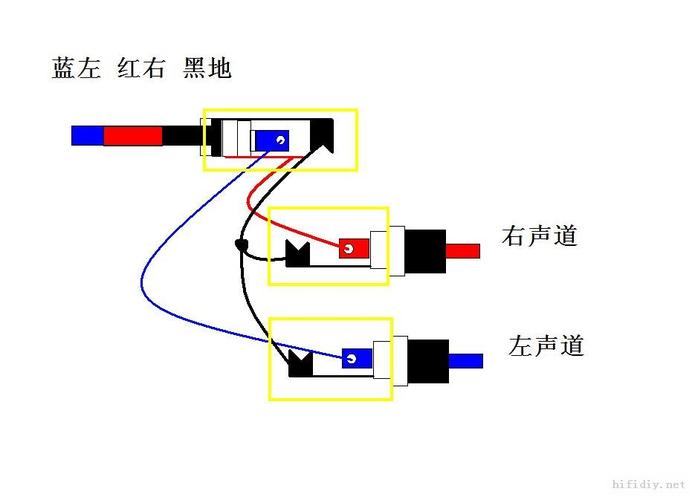

用 74LS153 设计一个一位全加器。--- 根据全加器的功能要求,写出真值表。全加器功能: C_S = X + Y + Z。真值表,放在插图中了。(用数据选择器设计时,卡诺图、化简、逻辑表达式,都是不需要的。

数据选择器构成全加器的优点是电路简单,缺点是有几个变量就要用几位的译码器,输出端可能有很大的浪费(比如四个变量组成的一个表达式)。用门电路优点是层次清晰,缺点是电路较为复杂,所需门电路元件多。

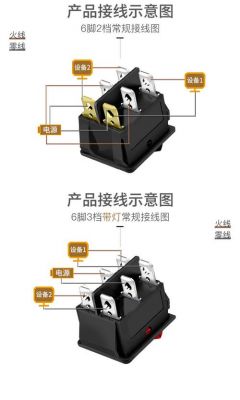

选择器2的使能G2接反向器的输出,选择器1的使能G1接反向器的输入. 这个输入做3路选择信号的C端,加上已经有的A,B,就可以了。根据全加器真值表,可写出和s,高位进位co的逻辑函数。

选一,肯定有3位使能端,abc,则把高位a=0,低两位bc作为两个加数 8位选通端的前四位作为和,并依次接0110电平。

表达式:F=A’BCD+AB’CD+ABC’D+ABCD’+ABCD,故,A、B、C分别接于74151的AAA0,D接于74151的DDD6,1接于74151的D7,0接于74151的D0、DDD4。

4位加法器能否作为3位加法器用?与输入的3位二进制数如何连接?共有多少...

位加法器是指能实现四位二进制数全加的数字电路模块,称之为4位全加器。4位加法器包括逐位进位 超前进位特点逻辑电路简单,但速度也较低释义四位二进制数全加的数字电路模块。

可以使用一块四位二进制加法器来实现两个三位二进制数相加。具体实现如下:将两个三位二进制数分别表示为 A 和 B,并且假设 A 的前三个字节为 a1,a2,a3,B 的前三个字节为 b1,b2,b3。

【答案】:①设F=(3x)=0X2X1X0+X2X1X00,四位加法器输入端P=0X2X1X0,Q=X2X1X00,输出COF3F2F1F0②Y=F/8=COF3F2F1F0/1000=COF3F2,再用一个四位加法器P=0000,Q=00COF3,F2直接作小数第1位输出。

如果用 4 位数值比较器比较两个 3 位二进制数,举例说出输入信号的接法 用 4 位的数值比较器,比较 3 位数,可以有 1 位空置,同时接地接高电平均可。

到此,以上就是小编对于全加器连接图的问题就介绍到这了,希望介绍的几点解答对大家有用,有任何问题和不懂的,欢迎各位老师在评论区讨论,给我留言。

微信扫一扫打赏

微信扫一扫打赏