本篇目录:

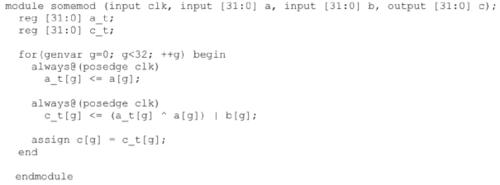

求verilog编写下面文件的测试信号

1、建立.v文件,文件名为 shift_tb.v ,这个就是仿真文件。

2、要实现将50MHz的输入信号分频输出4Hz,可以使用HDL语言(如Verilog或VHDL)编写代码来实现。

3、Verilog的TB文件是一种包含在设计环境中的,独立于所测试设计的Verilog代码文件。TB文件中包含了验证设计的测试描述、测试向量、检查点等信息。TB文件的编写过程可以分为三个主要部分:环境设置、测试向量编码和检查点设置。

verilog的tb文件怎么写

1、要测试这段代码,你需要准备一个测试文件。测试文件中需要定义输入信号、输出信号和测试用例。

2、比如你有一个TB模块,下面有A,B两个模块,如果你在B里头想用A的内部信号a1,则应该在B里头写:TB.A.a1。这样即使输入输出名字相同,也不会混淆。

3、方法如下:verilog中数据的写入分为三步: $fopen()打开文件。、$fwrite()写入相应data 。、$fclose()关闭文件。

关于verilog的仿真测试程序编写

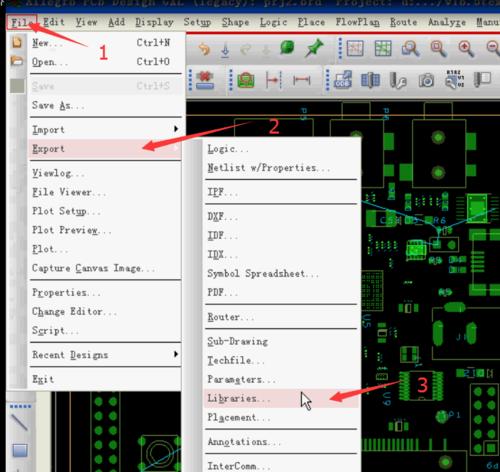

verilog用ALTERA软件编写vcs。如果只是仿真的话,可以使用modelsim;如果要对程序进行编译、综合、烧写且调试的话,可以使用altera公司的quartus ii和xilinx公司的ise软件。这几种软件我都用过,网上都可以下到相关的安装软件。

你自己建立一个波形编辑文件,在这里面可以自己编辑输入的波形的,然后仿真就可以看到了。波形是你可以随意编辑的,不写测试文件也可以啊,写比较麻烦,但是如果你要全面的测试的话几就要写了。

测试就是往DUT接口上加激励,通过DUT的输出判断是否正确。

请问 用什么软件来 编写verilog 语言?首先,应该是用什么软件来仿真 verilog语言描述的电路。

这就是把ABC三个电台的启动信号变为输入,XY的启动信号为输出,列出真值表就行了吧。

到此,以上就是小编对于verilog测试文件编写实例的问题就介绍到这了,希望介绍的几点解答对大家有用,有任何问题和不懂的,欢迎各位老师在评论区讨论,给我留言。

微信扫一扫打赏

微信扫一扫打赏