本篇目录:

请问一个时基电路555中在实际电路应该怎么连接

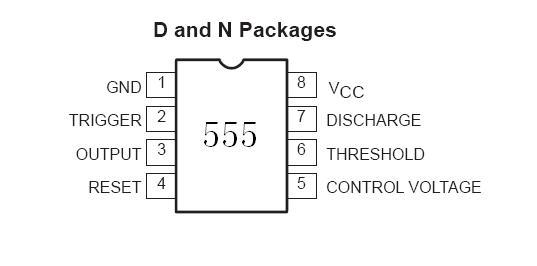

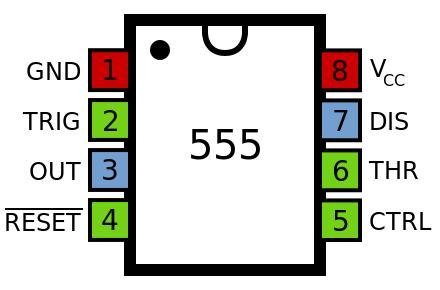

1、电路图中的1~8脚没有必要一定按照顺序排列,只是为了画图简洁。电路图中更多的表达是连接关系,而不是实际元件上引脚的位置关系。电路图中1脚对应的是555之8脚封装的第1脚,依次类推。

2、时基电路是555定时器与电阻、电容构成充放电电路,并由两个比较器来检测电容器上的电压,以确定输出电平的高低和放电开关管的通断。

3、脚优先,当2脚输入电压低于1/3VCC时,输出为高电平。此时6脚无效。(可能想问的是6脚冲突时的情况)冲突时,复位脚,即4脚优先,4脚为低电平时,输出一定是低电平,4和6脚不起作用。

4、脚为复位输入端,当为低电平时输出端3输出低电平,OC输出端7脚导通,而不管其它脚(5,6,2脚)处于什么电压。一般该脚连接电源,当然也可以用于控制输出。555基本的应用在震荡场合。

555定时器问题,求解答

1、定时器的最基本应用包括以下三种类型:单稳态触发器(Monostable multivibrator):在这个模式下,555定时器被配置为单稳态触发器或单谐振触发器。

2、定时器时间T=1*(R1+R2)*C(秒),如果取c=47uF=0.000047F 15秒=1*(R1+R2)*0.000047 R1+R2=290k 再取R1=100K R2为一个220K可调电位器就行就可以实现15秒计时电路。

3、多谐振荡电路的周期计算公式:f = 1 / T = 44 / (R1 + 2R2)*C。(注:其中f为频率、T为周期、R1,R2为电阻大小、C为电容容量大小。

555定时器实验中,第5管脚为什么要经一个电容接地?第4管脚为什么要接+5V...

一般是为了消除电路中的高频成分,因为电容器的容抗与电路信号的频率和电容器的电容量成反比,所以电容量一定时,对高频成分的容抗较低,容易经电容接地。或者要将低频接地,则要用大容量的电容。

脚:CO(或VC)为控制电压端。若此端外接电压,则可改变内部两个比较器的基准电压,当该端不用时,应将该端串入一只0.01μF电容接地,以防引入干扰。6脚:TH高触发端。7脚:D放电端。

图6—1 555定时器组成框图 它的各个引脚功能如下:1脚:外接电源负端VSS或接地,一般情况下接地。8脚:外接电源VCC,双极型时基电路VCC的范围是5 ~ 16V,CMOS型时基电路VCC的范围为3 ~ 18V。一般用5V。

到此,以上就是小编对于555芯片接口的问题就介绍到这了,希望介绍的几点解答对大家有用,有任何问题和不懂的,欢迎各位老师在评论区讨论,给我留言。

微信扫一扫打赏

微信扫一扫打赏