本篇目录:

- 1、Cadence详细资料大全

- 2、cadence软件

- 3、如何使用Cadence的LEC工具完成逻辑一致性验证

- 4、什么是“CADENCE”工具?

- 5、cadence软件有几种?

- 6、cadence使用总结

Cadence详细资料大全

1、原理图的绘制主要有以下几个步骤:原理图库的绘制。cadence中库中不可能将你若需要的器件都包括,所以学会库的制作很重要。原理图的绘制,根据你设计的电路,绘制原理图。

2、Cadence 是一个大型的EDA 软件,它几乎可以完成电子设计的方方面面,包括ASIC 设计、FPGA 设计和PCB 板设计。Cadence 在仿真、电路图设计、自动布局布线、版图设计及验证等方面有着绝对的优势。

3、cadence分为几个模块,通常指的是Design Entry CIS和PCB Editor。

4、打开PowerDC,新建Workspace。

cadence软件

1、cadence软件分2种,一个种是高端的Allegro配合Orcad的,另外一种就是只有Orcad,不管怎样,Orcad是一定有的。

2、Cadence芯片设计软件是一款集成电路设计软件。Cadence的软件芯片设计包括设计电路集成和全面定制,包括属性:输入原理,造型(的Verilog-AMS),电路仿真,自定义模板,审查和批准了物理提取和解读(注)背景。

3、AltiumDesigner:一款功能强大的PCB设计软件,可用于从原理图设计到PCB设计的全流程设计。Cadence:一款综合性的EDA软件,包括电路仿真、PCB设计、芯片设计等多个方面。

如何使用Cadence的LEC工具完成逻辑一致性验证

1、所有可以做的,就是证明一个系统没有任何可以想到的缺陷,并且满足所有的使系统符合功能要求的和有用的属性。

2、形式验证分类:等价性验证:其一RTL&netlist gate level,其二,gate level &gate level...基于模型的验证:时态逻辑模型规范,受电路规模的影响。

3、逻辑综合得到门级网表。4.门级验证(Gate-Level Netlist Verification)门级功能验证是寄存器传输级验证。主要的工作是要确认经综合后的电路 是否符合功能需求,该工作一般利用门电路级验证工具完成。

4、打个比喻来说,前端就像是做蓝图的,可以功能性,结构性的东西。而后端则是将蓝图变成真正的高楼。

5、首先是老板产生一个创意,然后就是设计人员(学生)使用vhdl或者是verilog语言对设计来进 行描述,生成hdl代码。

什么是“CADENCE”工具?

1、candence 为公司名 ,也会用candence 指他们公司一系列产品软件。 allegro为软件名:画pcb板用 ,orcad为线路图绘制工具,与allegro配合使用效果佳(同一公司产品)。

2、Cadence 公司是老牌的EDA工具提供商,采用Cadence的软件、硬件和半导体IP,用户能更快速向市场交付产品。

3、cadence软件分2种,一个种是高端的Allegro配合Orcad的,另外一种就是只有Orcad,不管怎样,Orcad是一定有的。

4、Cadence:Cadence公司是老牌的EDA工具提供商,采用Cadence的软件、硬件和半导体IP,用户能更快速向市场交付产品。Cadence的电路仿真软件的一个小缺点是,操作较为复杂,比较适合复杂板的开发。

5、cadence spectre是cadence针对全定制集成电路推出的仿真工具,主要用于模拟及数模混合集成电路的仿真。主要在unix工作站上使用。楼主可以用Hspice来替代它,进行仿真。

6、cadence orcad:是一套在个人电脑的电子设计自动化套装软件,专门用来让电子工程师设计电路图及相关图表,设计印刷电路板所用的印刷图,及电路的模拟之用。

cadence软件有几种?

cadence软件分2种,一个种是高端的Allegro配合Orcad的,另外一种就是只有Orcad,不管怎样,Orcad是一定有的。

SPICE是一个仿真的软件,用来电路方针。DRC的意思是设计过程中出现的错误,不是什么软件,和word里面的你输入了一些错字,word会自动在那些错字上面显示一个红色的标记一样。transient simulation是传输延迟,一个仿真方面的术语。

Concept HDL原理图设计输入工具,有for NT和for Unix的产品。Check Plus HDL原理图设计规则检查工具。

cadence使用总结

形式验证分类:等价性验证:其一RTL&netlist gate level,其二,gate level &gate level...基于模型的验证:时态逻辑模型规范,受电路规模的影响。

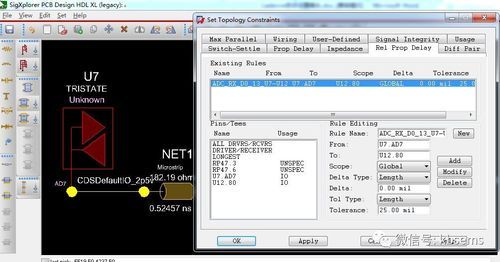

Cadence 是一个大型的EDA软件,可以完成电路设计的方方面面。本文以DSP最小系统为例(参照于博士教程),将区域约束流程Cadence12版本上的操作加以总结。

底层软体 Cadence 的底层软体有下面这些: 逻辑设计规划器 这是用于设计早期的规划工具。其主要用途是延时预测、生成供综合工具使用的线路负载模型。这个工具是用来在物理设计的早期象逻辑设计者提供设计的物理信息。

到此,以上就是小编对于cadence软件的问题就介绍到这了,希望介绍的几点解答对大家有用,有任何问题和不懂的,欢迎各位老师在评论区讨论,给我留言。

微信扫一扫打赏

微信扫一扫打赏