本篇目录:

fpga输出高电平准确为几V?

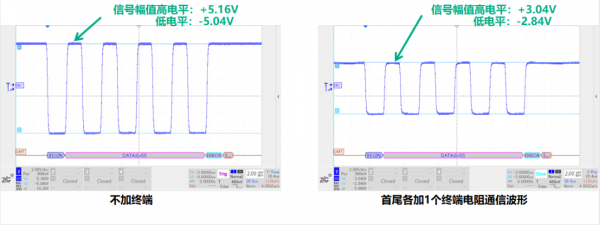

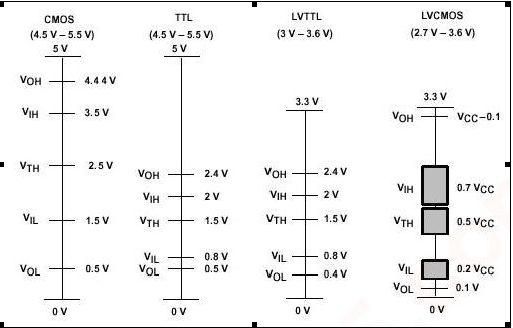

TTL输出高电平4V,输出低电平0.4V。在室温下,一般输出高电平是5V,输出低电平是0.2V。最小输入高电平和低电平:输入高电平=0V,输入低电平=0.8V,噪声容限是0.4V。

输出电平和具体FPGA的设置及外负载情况相关,如果输出悬空(无负载),如果楼主设成LVTTL的,并且VDDio电压给的3V,则高电平输出大约是1V,低电平约0.2V。如果设置为CMOS则高为3,低为0.0V。

FPGA的端口输出电平大都为0~3V的,升压复杂降压容易,在需要输出0~8V的输出端口上,设计上两个分压电阻就行了:220Ω+270Ω=490Ω,3V*270/490≈82V。

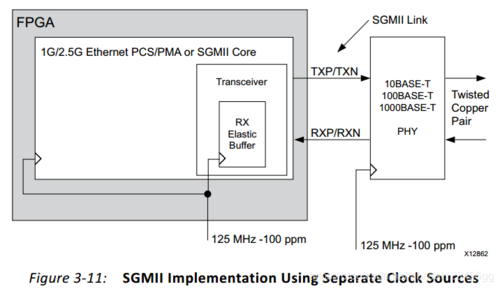

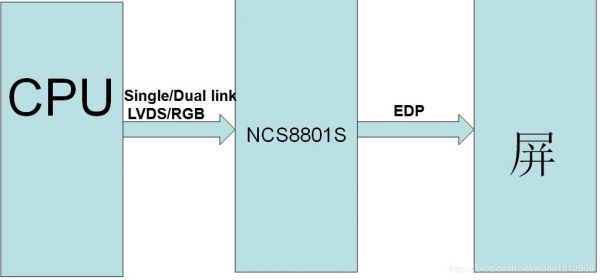

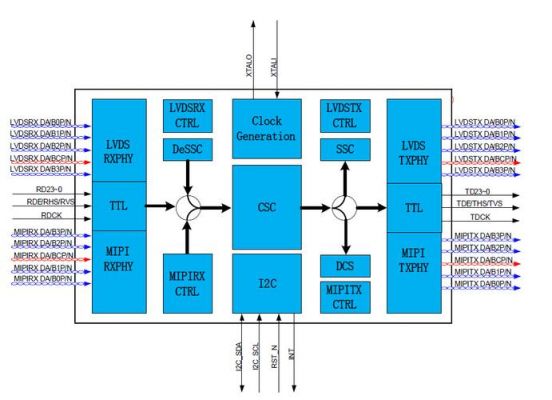

FPGA可以配置成各种电平,如:LVTTL、LVCMOS、LVDS等,不同电平输出高电平就是“1”,低电平就是“0”。

早期的FPGA有5V的供电引脚,因此IO可以是5V/3V的;而现今大多数FPGA的供电都只有3V以下了,所以其IO引脚也只能提供3V以下的输出了,但有不少FPGA仍然容许输入5V的高电平(具体情况需要阅读相应型号FPGA的说明书)。

接了5V 5V左右的信号会被判为高;接8V 2V左右的信号判为高。所以FPGA BANK区电压怎么配置电平最主要的就是看接到这个BANK区的另外一个器件的输出输入(或叫IO)电平。

FPGA输入电压是多少认为是高电平

1、TTL输出高电平4V,输出低电平0.4V。在室温下,一般输出高电平是5V,输出低电平是0.2V。最小输入高电平和低电平:输入高电平=0V,输入低电平=0.8V,噪声容限是0.4V。

2、FPGA BANK区的电压不能瞎接,接了3V,2V以上的信号就会判为高;接了5V 5V左右的信号会被判为高;接8V 2V左右的信号判为高。

3、输出电平和具体FPGA的设置及外负载情况相关,如果输出悬空(无负载),如果楼主设成LVTTL的,并且VDDio电压给的3V,则高电平输出大约是1V,低电平约0.2V。如果设置为CMOS则高为3,低为0.0V。

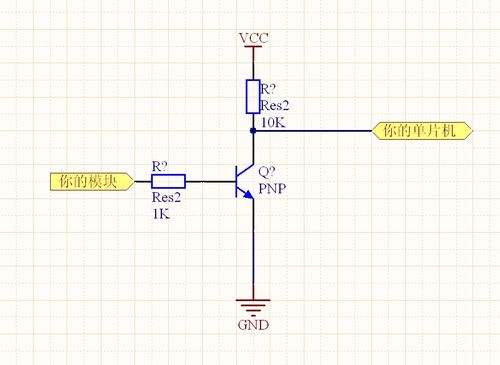

4、理论上可以的,L298N的数据手册上说VH只要大于3V就可以了。但一般不这样用,你想想去驱动步进电机,地上多大的地弹,最好还是采用光耦隔离。

5、OH)。在负载合理范围内,视供电电压不同而不同,视端口类型不同而不同。一般3V供电,最常见的通用IO口(CMOS工艺),手册写端口输出高电平最低为9V,实际一般测量大多是2V多一点。还有些特殊端口是VCC-0.4V。

fpga的io角是不是都是3.3v的

1、一般3V供电,最常见的通用IO口(CMOS工艺),手册写端口输出高电平最低为9V,实际一般测量大多是2V多一点。还有些特殊端口是VCC-0.4V。

2、FPGA的端口输出电平大都为0~3V的,升压复杂降压容易,在需要输出0~8V的输出端口上,设计上两个分压电阻就行了:220Ω+270Ω=490Ω,3V*270/490≈82V。

3、首先是可以直接互相连接的,这关系到一个规范的问题最直接的方法就是直接互连,这个不会有太大的问题,因为我作过类似的事情,但这样并不好,因为单片机是5V的IO,而FPGA的IO一般都是3V。

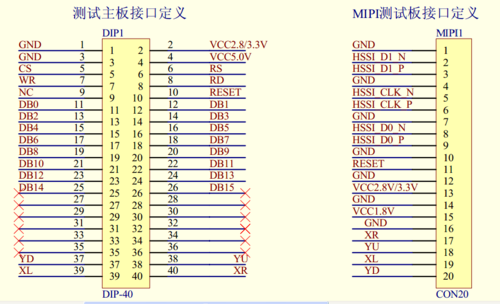

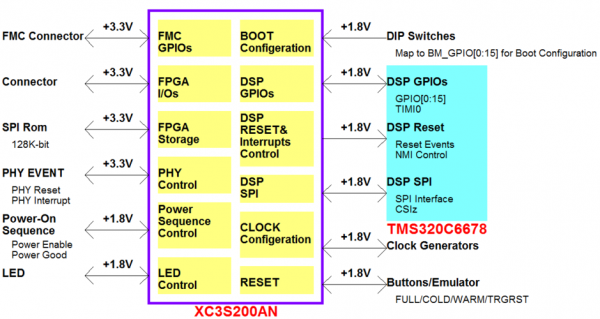

4、FPGA的供电基本都有核心电压(VCCINT)和IO电压(VCCIO)两种,有些FPGA还有其他辅助电压,如VCCAUX,VBAT等。核心电压是FPGA内部逻辑运行需要的电压,不全是2V,由芯片的制造工艺而定,需要查阅具体的数据手册。

5、vcc、gnd该接的都接好,晶振连接到固定的时钟管脚,剩下的基本上也就是IO了,IO你可以随便使用的,最好是将同一类型的信号管脚连接到FPGA同一个bank中,这样FPGA布局布线的效率会很高。

6、这个需要在你的工程中对管脚进行约束的,如果约束好了的话,你就需要检查自己硬件板上的FPGA电源和地整对了没?另外,管脚电平水平也不是随便可以满足的,具体看一下芯片资料吧。

到此,以上就是小编对于fpga lvds ip核的问题就介绍到这了,希望介绍的几点解答对大家有用,有任何问题和不懂的,欢迎各位老师在评论区讨论,给我留言。

微信扫一扫打赏

微信扫一扫打赏