本篇目录:

- 1、Quartus设计一个带有同步清零端、同步置数端的JK触发器并编译仿真,用原...

- 2、quartus多个时钟脉冲输入可以功用一个管脚吗

- 3、求quartus2的详细使用方法

- 4、rs触发器quartus用什么芯片

- 5、如何测量一个D触发器的延时,QuartusII仿真

- 6、如何在quartus中使用T触发器

Quartus设计一个带有同步清零端、同步置数端的JK触发器并编译仿真,用原...

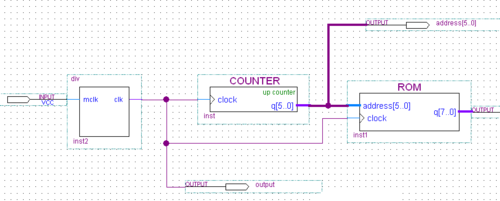

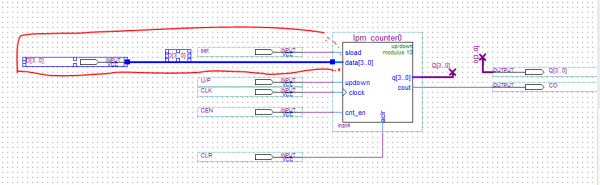

1、①=0时异步清零,C0=0 ②=1,=0时同步并行置数 ③==1且CPT=CPP=1时,按照4位自然二进制码进行同步二进制计数。④==1且CPT·CPP=0时,计数器状态保持不变。

2、用jk触发器设计一个三进制计数器,计数是00,01,10,这三个数,所以,只需两个JK触发器就行,不需要3,用了3个,也有一个触发器的状态始终0,也没有用。

3、预置输入先置0,取Q(N)的输出做置数信号,在(N+1)的时钟前沿Q输出同步归零,这是完全同步计数,是同步计数器的正确用法。

4、可以用同步4位二进制加法计数器74LS16三输入与非门74LS451共阴七段数码LED显示器来实现七进制的计数器。

quartus多个时钟脉冲输入可以功用一个管脚吗

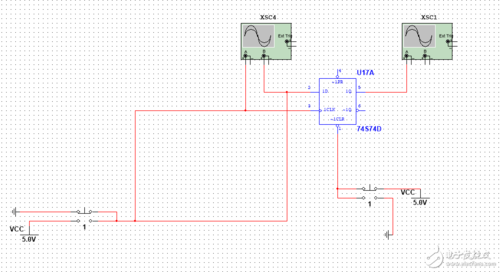

时钟信号输入端CLOCK接时钟输入信号,这样每来一次CLOCK脉冲,D触发器的状态就会翻转一次,每两次CLOCK脉冲就会使D触发器输出一个完整的正方波,这就实现了2分频。

PLL的时钟输入 专用时钟输入管脚(1)÷n计数器 areset areset是高有效信号,复位所有的PLL计数器为初始值。当该信号为高时,PLL复位该计数器,失锁。一旦该信号再次变低时,锁定过程开始,PLL重新和输入参考时钟同步。

pins:选择为As input tri-stated。

求quartus2的详细使用方法

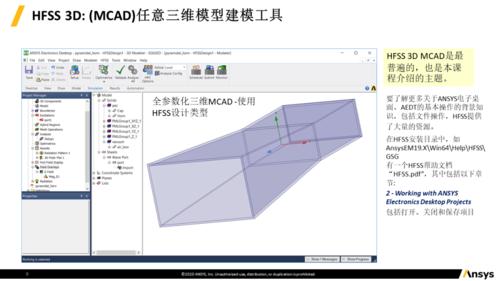

在这里,首先用最简单的实例向读者展示使用Quartus II软件的全过程。进入WINDOWS XP后,双击Quartus II图标,屏幕如图1所示。

使用方法如下,首先需要打开QuartusII应用程序,并且选择创建新工程按钮。接着是不需要进行修改任何参数的,直接 点击下一步。然后修改保存路径及工程名称。接着选中加进去的文件名,点击下一步就好了。

双击打开QuartusII软件,选择 file---New Project Wizard...弹出如下窗口,本窗口介绍创建一个工程需要执行的设置,点击next。

rs触发器quartus用什么芯片

C390,C420,C450。rs触发器芯片的产品品种比较少,只找到早期上海无线电十四厂生产的几种rs触发器芯片,其型号分别是C390,C420,C450,它们都是四rs锁定触发器。

LS161是一种具有3个8位二进制计数器、3个基本RS触发器和1个时钟控制器的芯片。该芯片的引脚功能如下:CP0:时钟输入端,用于输入时钟信号。Q0~Q2:三个8位二进制计数器的输出端,用于控制三个基本RS触发器的状态。

LS74是D触发器,功能多,可作双稳态,寄存器,移位寄存器,振荡器,单稳态,分频等。

不可以,altera公司生产的软件是quartus,配套的altera硬件常用的有cyclone等;与xilinx的芯片相配套的是foundation或者ISE软件 总之,一个公司的硬件和软件要配套使用。

RS触发器一般用来抵抗开关的抖动。为了消除开关的接触抖动,可在机械开关与被驱动电路间接的接入一个基本RS触发器,如图1所示838电子。S=0, R=l,可得出A=l, A‘=0。

RS422/RS485的接口芯片知如下:产品对比:RS422是一个四线双端口(两线接收端口和两线发送端口)。只有一个主人。主机的发送端口连接到所有从机的接收端口。主机的接收端口连接到所有从机的发送端口。

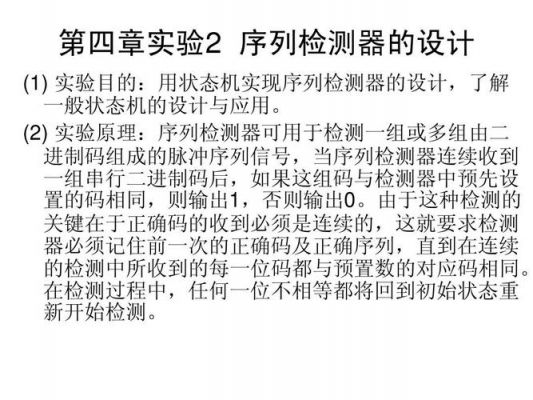

如何测量一个D触发器的延时,QuartusII仿真

)选中clk,在工具栏中点击Overwrite Clock按钮,打开图示对话框,将CLK周期设置为50ns。2)将clr设置为“0”(在波形图左边竖着的有个0矩形波)。

你再仿真的对话框里,也就是simulator那里,将最上面的下拉菜单点开,timing表示时序仿真,function表示功能仿真。另外,选择功能仿真后要先按一下右侧的generate按钮,再点start按钮。

这个的意思是说你在仿真以前要至少要进行Analysis and Synthesis才能够sunmulate。解决方法是对你的工程编译一次就可以,只要修改过,就要重新编译一下。编译完就可以sunmulate。

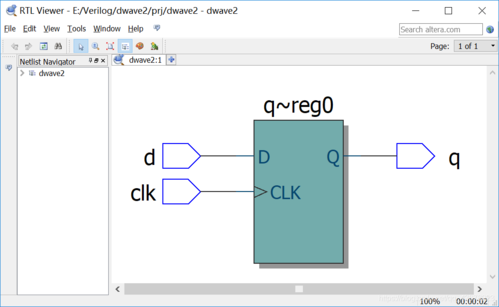

在Quartus 2里面是有D触发器的。寻找方法:选择insert symbol-primitives-storage-dff,就能找到。

每个电子器件都有延时;你做的是时序(timing)仿真,可以设置成功能仿真(functional),这样就没延时了。是软件不考虑延时,实际中还是有延时的。

实验条件计算机;QuartusII开发平台;ME5000EDA实验箱(备选);实验步骤创建工程;用VHDL语言设计一个D触发器。

如何在quartus中使用T触发器

T触发器(Toggle Flip-Flop,or Trigger Flip-Flop)设有一个输入和输出,当时脉由0转为1时,如果T和Q不相同时,其输出值会是1。

T触发器就是只要输入端T为高平,来一个出发脉冲输出就反一下(变成原来的非);如果T为低平则不变。把Q非端和D连接。Q非为1且Q为0时,来一个脉冲Q将变为1且Q非变为0;再来一个脉冲又反过来。

D触发器构成T触发器 D=TQ(Q为反)+T(T为反)Q 转换方式如下:D触发器的状态方程是:Q*=D,JK触发器的状态方程是:Q*=JQ'+K'Q。

到此,以上就是小编对于Quartus的D触发器如何异步置零的问题就介绍到这了,希望介绍的几点解答对大家有用,有任何问题和不懂的,欢迎各位老师在评论区讨论,给我留言。

微信扫一扫打赏

微信扫一扫打赏