本篇目录:

- 1、SPI上升沿和下降沿读取数据的区别

- 2、根据spi时序图如何写verilog,谢谢

- 3、ISD4004的SPI(串行外设接口)

- 4、SPI总线协议需要了解哪些知识点?

- 5、看SPI时序图,怎么确定该器件是第一个时钟周期采集数据还是第二个时钟...

SPI上升沿和下降沿读取数据的区别

1、上升沿和下降沿判断方法如下:上升沿就是触发的那一瞬间,就是开关闭合的那一瞬间有效,由零变为一的那一下叫上升沿,反之由一变为零的那一瞬间叫下降沿,正常接通以后没有电平变化不起作用。

2、上升沿是指信号电平从低电平向高电平转变的那一段时间。可以理解为信号波形上由低电平开始到高电平结束的这一部分。其中:t1表示信号从低电平开始的时间,t2表示信号达到高电平的时间,T表示上升沿的持续时间。

3、数字电路中,数字电平从低电平(数字“0”)变为高电平(数字“1”)的那一瞬间(时刻)叫作上升沿。硬件描述语言 在Verilog等硬件描述语言中,用“posedge”表示“上升沿”。

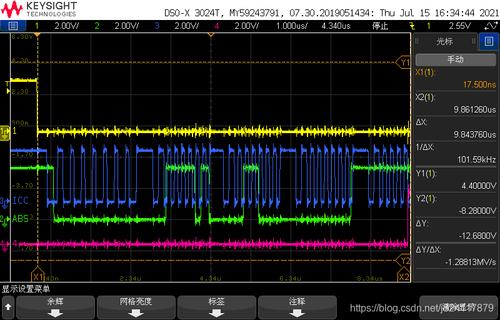

根据spi时序图如何写verilog,谢谢

时序可以通过状态机实现,将时序分为不同的状态,比如idle,开始,传地址,传数据,结束等等,然后通过不同的条件进行状态转换。这是简单的时序实现,复杂的话,不是这里能说明白的,还是看书吧。

按照SPI的时序写驱动程序就可以了,最好事先设计好模块。

首先你的题意表达得非常不清楚(DATA没说位数,不知道DATA的输出具体是什么),只根据你这个时序图看,各个信号都是输出(每个信号处都标明有o输出除了WAIT是i输入以外)这明明就是个测试波形,写出的文件就是testbench。

你可以把SCL进行8分频、9分频的,这样SCL和BCLK是同步的,识别到SCL沿时,用8个BCLK传输数据即可。建议查看下I2C\I2S\SPI等类似的协议和代码,对于你理解完成Verilog编写代码会有很大帮助和指导的。

这个要看你的外挂SPI的芯片具体型号,SPI接口也有8位,12位,16位,24位等等的。程序都有些不一样。而且这样直接求代码,一般是求不到的。虽然是个简单的代码。

ISD4004的SPI(串行外设接口)

ISD4004 工作于SPI 串行接口。SPI 协议是一个同步串行数据传输协议,协议假定微控制器的SPI 移位寄存器在SCLK 的下降沿动作,因此对ISD4004 而言,在时钟止升沿锁存MOSI 引脚的数据,在下降沿将数据送至MISO 引脚。

ISD1700系列好,ISD1700是在ISD400ISD2500、ISD1400基础上发展起来的,便宜且易于控制。ISD4004和ISD2560是将要淘汰的产品,就别去研究了。ISD4004有SPI接口,可以串行控制;而ISD2560没有,只能并行控制。

STC89C52单片机的P1(TXD)接ISD4004语音芯片的串行时钟(SCLK)的时钟输入端(8引脚),而数据的输入输出则由P0(RXD)控制。

SPI总线协议需要了解哪些知识点?

CPOL=0,串行同步时钟的空闲状态为低电平;如果CPOL=1,串行同步时钟的空闲状态为高电平。时钟相位(CPHA)能够配置用于选择两种不同的传输协议之一进行数据传输。

三线制:三线制SPI总线使用MOSI、MISO和SCK三条线进行数据传输。在三线制中,数据是双向传输的,MOSI线用于主设备向从设备发送数据,MISO线用于从设备向主设备发送数据。时钟线(SCK)用于主设备和从设备之间的同步。

先了解三点 SDO是MISO,指主器件数据输入,从器件数据输出;SDI是MOSI,指主器件数据输出,从器件数据输入。SPI是全双工,从高位开始。上升沿还是下降沿,由设备决定。

通讯是通过数据交换完成的,这里先要知道SPI是串行通讯协议,也就是说数据是一位一位的传输的。这就是SCK时钟线存在的原因,由SCK提供时钟脉冲,SDI,SDO则基于此脉冲完成数据传输。

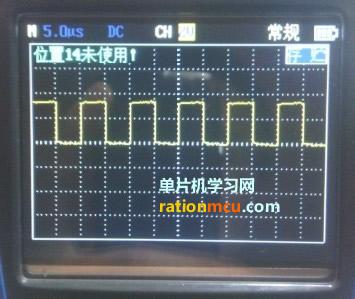

看SPI时序图,怎么确定该器件是第一个时钟周期采集数据还是第二个时钟...

1、CPHA=0:数据从第一个时钟(SLCK)边沿开始采集CPHA=1:数据从第二个时钟(SLCK)边沿开始采集Ok,理解CPOL和CPHA基本概念以后,下面这两个要开始”合体”了。CPOL和CPHA合体就形成了SPI四种模式。声明:部分图片源自网络,并非原创哈。

2、在此,我们可以先不读出它的数据的状态或者数据本身。

3、SPI接口 串行外围接口一共有4种操作模式,图3为其时序图。这些操作模式决定了传送与接收的时钟相位和极性,换句话说,也就是这些模式决定了利用时钟信号的哪个沿来控制数据传判断的方向。这些模式一般由主机(CPU)来设置。

4、数据将会是sdo=1;寄存器=0101010x。下降沿到来的时候,sdi上的电平将所存到寄存器中去,那么这时寄存器=0101010sdi,这样在 8个时钟脉冲以后,两个寄存器的内容互相交换一次。这样就完成里一个spi时序。

5、为由浅入深,假设 Skew = 0,即说明时钟到达所有器件的时间相同,没有差异,那么图中时钟上升沿1到时钟上升沿2之间刚好相隔一个工作周期T。下面介绍几种情况下的同步时序电路模型的时序图,图中标注了说明。

6、对于一些设备,只要从设备被选择,从设备数据输出引脚输出的数据的第一位是有效的,在这种格式中,在/SS引脚变低后的半个时钟周期就产生第一个跳变沿。

到此,以上就是小编对于标准SPI时序图的问题就介绍到这了,希望介绍的几点解答对大家有用,有任何问题和不懂的,欢迎各位老师在评论区讨论,给我留言。

微信扫一扫打赏

微信扫一扫打赏