本篇目录:

VHDL是什么

VHDL的全称是Very-High-Speed Integrated Circuit Hardware Description Language,是一种用于设计硬件系统的描述语言。VHDL看起来与软件编程语言有些相似,但本质上有很大不同。

VHDL 就是 VHSIC Hardware Description Language 的缩写,而 VHSIC 就是 Very High Speed Integrated Circuit 的缩写,其意义就是非常高速积体电路。所以 VHDL 就是非常高速积体电路的硬体描述语言。

VHDL语言是一种用于电路设计的高级语言。它在80年代的后期出现。最初是由美国国防部开发出来供美军用来提高设计的可靠性和缩减开发周期的一种使用范围较小的设计语言 。

一种硬件描述语言(HDL),英文全称为Very High Speed Integrated Circuit Hardware Description Language ,超高速集成电路硬件描述语言。

vhdl:是一种用于电路设计的高级语言。verilog:是一种硬件描述语言。来源不一 vhdl:诞生于1982年,来自ADA。verilog:是由Gateway设计自动化公司的工程师于1983年末创立,来自C语言。

什么是VHDL

1、VHDL 就是 VHSIC Hardware Description Language 的缩写,而 VHSIC 就是 Very High Speed Integrated Circuit 的缩写,其意义就是非常高速积体电路。所以 VHDL 就是非常高速积体电路的硬体描述语言。

2、VHDL是超高速集成电路硬件描述语言Very High Speed Integrated Circuit Hardware Description Language的英文缩写。

3、VHDL的全称是Very-High-Speed Integrated Circuit Hardware Description Language,是一种用于设计硬件系统的描述语言。VHDL看起来与软件编程语言有些相似,但本质上有很大不同。

4、所以 VHDL 就是非常高速积体电路的硬体描述语言。这是一项原由美国国防部 ( DoD, Department of Defense) 所支持的研究计画。为了将电子电路的设计意涵以文件方式保存下来,以便其它人能轻易地了解电路的设计意义。

5、一种硬件描述语言(HDL),英文全称为Very High Speed Integrated Circuit Hardware Description Language ,超高速集成电路硬件描述语言。

计算机硬件描述语言(VHDL)与编程语言(C语言)的区别及关系,

1、首先说VHDL:它是描述电路的计算机工具,早期的CPLD等器件是基于与-或阵列的,更容易说明这点,VHDL是描述电路行为的,当下载到器件后,它就是具体的电路,这个电路全由与-或阵列组成。

2、两个语言没有什么联系。前者是面向硬件的,有点类似单片机。一个是面向软件的,是计算机编程。语法结构没什么大的相似。都是编程语言。如果你要制造一个定时炸弹的定时系统,VHDL适合。

3、VHDL是硬件描述语言,用来做硬件设计的;C语言是软件编程语言,用来编写软件程序的。一个是用来设计硬件系统的,一个是用来设计软件系统的,用途完全不同,不可同日而语。

求教VHDL代码详细注释

VHDL是较常用的硬件描述语言。它的主要功能就是对硬件进行“逻辑”表达。

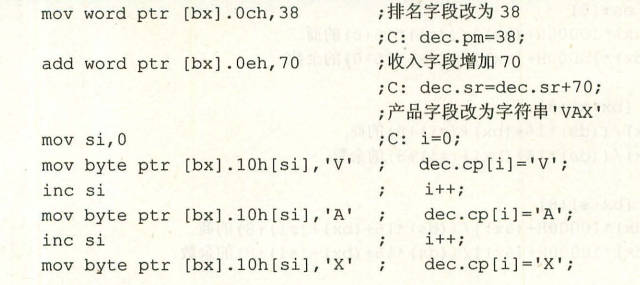

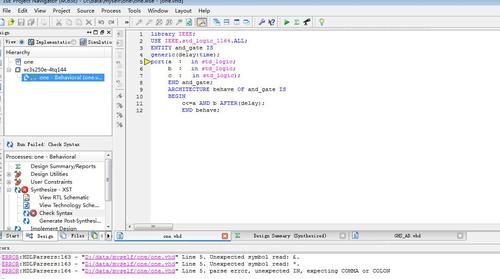

【答案】:格式:--注释内容 “--”断续划线,该划线是注释符,注释符右边的英文或中文均无语言意义,只起注释作用,帮助记忆或帮助阅读。

此为一个偶效验电路,就是检测输入的数据中有多少个1,偶数个则输出为0 奇数个则输出为1。程序在process中运行 遇到loop时循环loop,完成0到7的循环后结束,并赋值给Y。在循环中TMP与A的每一位经行异或并赋值给TMP。

你的问题在于对EVENT属性的运用,这个属性只对PS2INTERUPTION的变化沿敏感,而且不能同时和其他并列,因为沿是一个瞬间,其他可以等效成永远,这种选择关系本身就矛盾,所以无法综合。

这个要看你用的什么编辑器了,一般来说,如果是FPGA公司的开发环境软件(QUARTUS,ISE等),都是自带多行注释功能的,左键选中多行,右键里就有这个选项。

计数器就是数时钟上升沿的数目,0,1,10,11,100,101,110,111,1000……到32后再回到0。要改变对应引脚的频率的话,换成其它位数的计数器,比如33位的,34位的,最高的位的频率会变慢。

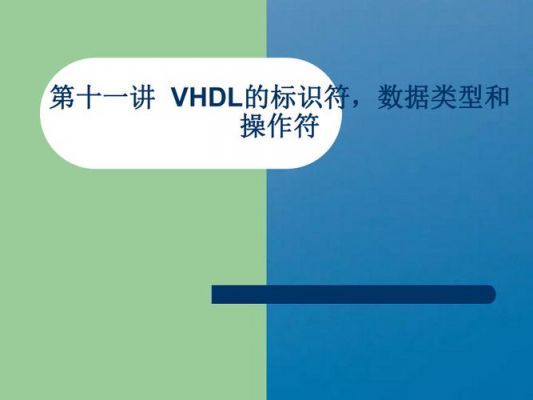

VHDL由哪四部分构成?

实体,结构体,库,程序包,配置 实体:用于描述所设计系统的外部接口特性;即该设计实体对外的输入、输出端口数量和端口特性。

vhdl进程由实体、结构体、库、程序包和配置五部分组成。VHDL语言是一种用于电路设计的高级语言。出现在在80年代的后期,最初是由美国国防部开发出来供美军用来提高设计的可靠性和缩减开发周期的一种使用范围较小的设计语言。

实体(ENTITY),实体的作用是给出实际电路的外部视图(引脚的数目,引脚的作用等),它描述了电路的封装结构 端口(PORT),在VHDL语言里的端口指的就是电路引脚,而非普通软件程序设计语言意义上的进程所拥有的端口。

标准设计库:std,用户现行工作库:work,IEEE设计库:IEEE。设计库由若干程序包组成,每个程序包都有一个包声明和一个可选的包体声明。在设计库中,包声明和包体声明是分别编译的。

(1)与其他硬件描述语言相比,VHDL具有以下特点:(2)功能强大、设计灵活。(3)强大的系统硬件描述能力。(4)易于共享和复用。

到此,以上就是小编对于vhdl的基本标识符是怎样规定的的问题就介绍到这了,希望介绍的几点解答对大家有用,有任何问题和不懂的,欢迎各位老师在评论区讨论,给我留言。

微信扫一扫打赏

微信扫一扫打赏