本篇目录:

verilog中用case语句时一定要用always块吗

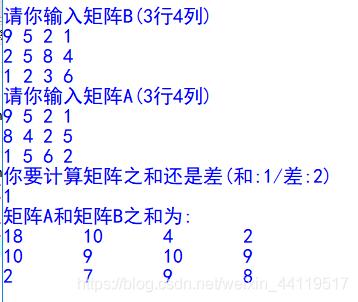

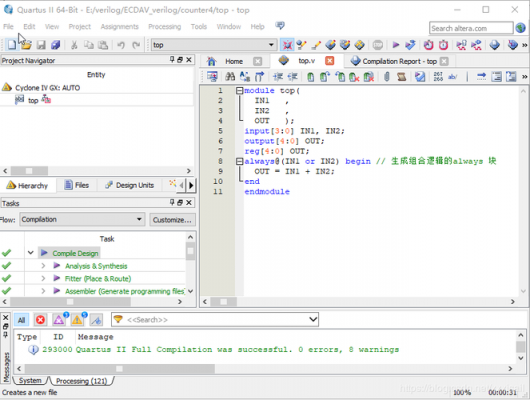

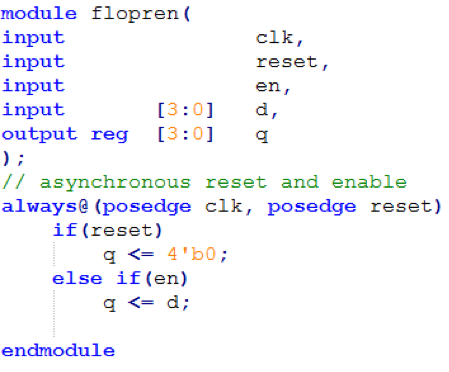

这是Verilog代码中的一段,其中使用了always关键字定义了一个模块,并使用case语句进行判断语句。它根据{a,b}参数中的不同组合值,进行赋值操作,并对count_cmb进行相应的修改。

兄弟,在verilog语法里有两种语句模块:一种是always块 ,另外一种是assign块 无论你写什么 ,多需要写在这个两个块里。否则是不被承认的,是没有“名分”的。

组合逻辑的case最好要有default,因为如果你的case不全,就会产生锁存器。及时你的case都包含全了,但是还是建议加上default,因为万一你哪天该代码,把某个case给去掉了,就会产生隐含的latch。所以,最好加上default。

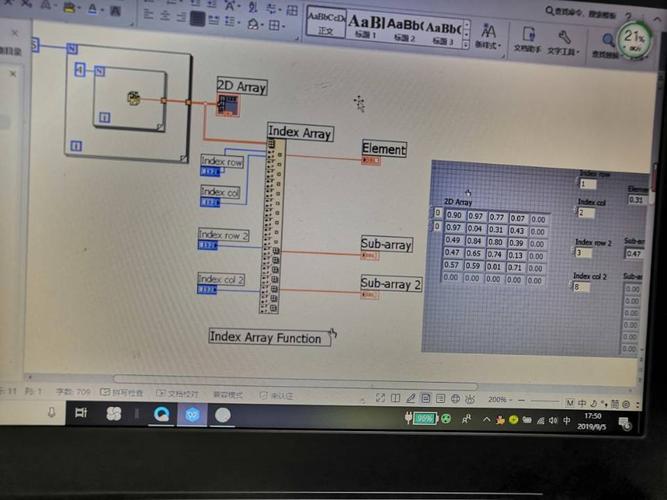

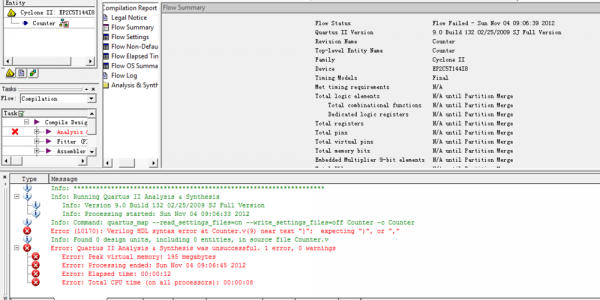

创建好后,在下方切换到Files面板,双击打开该文件,按照自己喜欢的形式输入数据。数据文件写好后,在项目上右键,点击New Source,接着选择Verilog Test Fixture,输入文件名并继续,选择待测模块,接着创建文件。

verilog中的case语法使用,求助!

1、这是Verilog代码中的一段,其中使用了always关键字定义了一个模块,并使用case语句进行判断语句。它根据{a,b}参数中的不同组合值,进行赋值操作,并对count_cmb进行相应的修改。

2、首先,右键单击项目并单击NewSource以创建一个新的代码文件。选择用户文档创建一个自定义文档文档,文件名和后缀随意。创建完成后,切换到文件面板底部,双击打开文件,根据自己喜欢的形式输入数据。

3、在Verilog中,if语句和case语句是两种不同的条件控制结构。if语句适用于具有单一条件的情况,而case语句适用于具有多个条件的情况。

4、在这里不能以C语言的语法来理解这段逻辑,应该考虑case语句在verilog里面综合完之后生成的什么电路。case语句是分支比较语句,也就是说,本质上就是case后面括号中的值与下面每个分支开头的值作比较,相同则执行。

5、我猜你想问的是case (条件)1:2:上面***是不是只能执行一条语句,是吗?答案是,不是,可以执行很多语句。你用begin--end括起来就可以了。

6、一个块下的case语句的各种情况。比如 case(x)1:2:3:...都是并行的,同时判断每个情况是否执行,而不是依次判断。就是每个情况都单独耗费了器件。

verilog的CASE用法?

1、写完数据文件后,右键单击项目,单击NewSource,然后选择Verilog测试装置,输入文件名并继续,选择要测试的模块,然后创建文件。双击打开文件,可以看到要测试的模块块的输入对应一些reg寄存器类型,输出对应一些wire类型。

2、在Verilog中,if语句和case语句是两种不同的条件控制结构。if语句适用于具有单一条件的情况,而case语句适用于具有多个条件的情况。

3、在这里不能以C语言的语法来理解这段逻辑,应该考虑case语句在verilog里面综合完之后生成的什么电路。case语句是分支比较语句,也就是说,本质上就是case后面括号中的值与下面每个分支开头的值作比较,相同则执行。

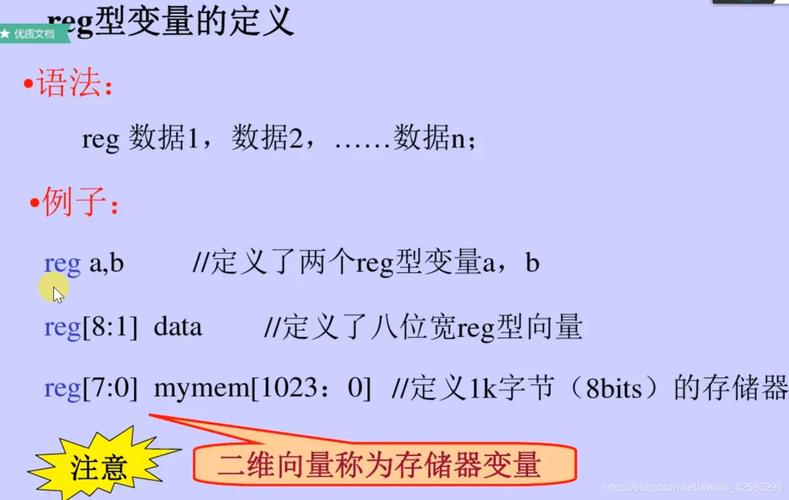

4、always里面的被赋值变量必须是reg型,这是语法的规定,只能遵守。写代码的时候不要加入触发器(不要边沿触发),最终综合出来的仍然是一个组合电路。case也注意要加上default,不然会综合一个存储器出来。

5、比如select = 8b1111_0101;那么select[1:2]为 10。如果【待定值】等于case中的select[1:2](10),那么这条case语句就被执行。

verilog里if语句中可以加入case吗?

1、写代码的时候不要加入触发器(不要边沿触发),最终综合出来的仍然是一个组合电路。case也注意要加上default,不然会综合一个存储器出来。

2、基本的语法都不通,非阻塞赋值是综合成寄存器的,需要在时钟的沿触发,不能写成组合逻辑。

3、功能差不多,if else有优先级,case没有,一般类别少的用if else,类别多用case。

4、在代码的第二个 case 语句中,如果 {a, b} 的状态为 A0, B0、B0, C0 或 C0, D0,则对变量 count_cmb 进行赋值,使其加一。

5、if(code[1])if(code[0])result = 8h08;else result = 8h04;else if(code[0])result = 8h02;else result = 8h01;else end endmodule 工作原理 使用Verilog描述硬件的基本设计单元是模块(module)。

6、case语句在条件比较简单的情况下适用,诸如a=1,2,3,4,5,..等等。if else 语句基本上可以处理所有的复杂判定条件,但是在实际电路中占用更多的资源。所以如果可以用case语句的话尽量用case语句。

到此,以上就是小编对于verilogcase语句举例的问题就介绍到这了,希望介绍的几点解答对大家有用,有任何问题和不懂的,欢迎各位老师在评论区讨论,给我留言。

微信扫一扫打赏

微信扫一扫打赏