本篇目录:

翻译(会有追加分),谢谢!!

1、I was in fancy of such a scene:我坐在一个有着很大落地窗的书店里,阳光洒进来,我坐在椅子上看书。

2、它不再需要使用-O5论据编译器(人士)使SLP协议的行为。Verilog加速度,只有-O5论据模拟器(asim)是必需的。在以前的版本,-O5 Active-HDL asim理由使得只有时机和SLP协议加速运算量模拟。

3、关节功能)。与流行的信念相反,一些肌肉纤维不能通过增加运动;相反,肌肉细胞只得到更大。肌肉纤维有能力有限增长肥厚和一些相信他们分裂增生如果通过主体的需求增加。恩呢,希望我能帮到你。

modelsim怎么自动生成testbench

首先是可以自动生成的,但是需要你自己添加你所需要的测试环境。其次建议使用modelsim-altera因为这是跟quartus ii无缝结合的。

“产生testbench 的步骤: processing - start - start testbench template writer 然后quartus II会自动编译生成testbench模板的 ”我的项目中激励就是个时钟,填写模板就该行了。试试。。

entity testbench is --一个空的实体,没有输入和输出。

方法1:为双向端口设置中间变量inout_reg作为该inout的输出寄存,inout口在testbench中要定义为wire型变量,然后用输出使能控制传输方向。

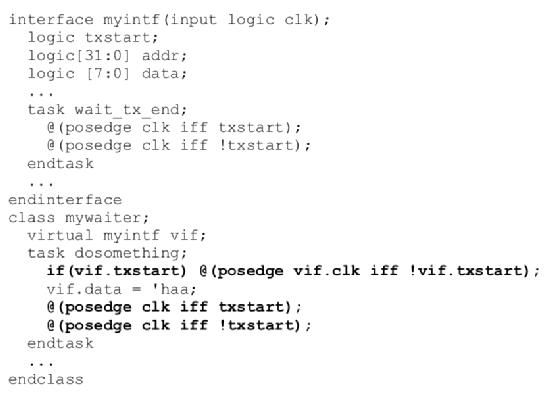

systemverilog设计哪方面的,学习要具备哪方面的基础知识啊

数字逻辑是任何电子电气类专业的专业基础知识,也是必须要学好的一门课。如果不能将数字逻辑知识烂熟于心,养成良好的设计习惯,学FPGA到最后仍然是雾里看花水中望月,始终是一场空的。

如果没有数字电路基础的话建议首先学一些基本的数字电路知识。然后看书,《Verilog HDL数字设计与综合》,一定注意只要看能够综合的代码,那些不能综合的东西可以一带而过。实践!实践!实践!光看书绝对学不会。

系统级(system):用高级语言结构实现设计模块的外部性能的模型。算法级(algorithm):用高级语言结构实现设计算法的模型。RTL级(Register Transfer Level):描述数据在寄存器之间流动和如何处理这些数据的模型。

编程语言 。IC 测试工程师需要学习相应的编程语言,例如:SystemVerilog,最好也要懂 C 和 C++。除了这些编程语言之外,还需要掌握 MATLAB 和 C 语言用来产生测试数据。验证语言 。

assign语句赋值特点

1、如果你确切的指明了敏感信号列表并且漏掉了一个信号,综合时也会被视为(*),但是模拟仿真将不会,并且不会和硬件相匹配。(在SystemVerilog中,使用always_comb)。

2、assign,我一般视其为“连线”语句。y只能是wire或output等导线型信号,不能是reg类型。因为寄存器的赋值是需要触发信号的,赋值时需要触发信号,而assign并不能提供触发信号,assign只能做导线连接操作。

3、assign L=(A&~SEL)|(B&SEL);//连续赋值 在assign语句中,左边变量的数据类型必须是wire型。input和output如果不特别声明类型,默认是wire类型。

4、Object.assign方法的第一个参数是目标对象,后面的参数都是源对象。注意,如果目标对象与源对象有同名属性,或多个源对象有同名属性,则后面的属性会覆盖前面的属性。如果只有一个参数,Object.assign会直接返回该参数。

5、assign表示连续赋值,且被赋值的变量只能是wire型的。

6、get :返回和字符串同名的变量的值 assign :将字符串变量的字符进行复制 get和assign是互为镜像的两个函数。这样在环境中,就生成了100个变量,分别为 data_1到data_100。

到此,以上就是小编对于verilog仿真器的问题就介绍到这了,希望介绍的几点解答对大家有用,有任何问题和不懂的,欢迎各位老师在评论区讨论,给我留言。

微信扫一扫打赏

微信扫一扫打赏