本篇目录:

- 1、求一个fpga高速信号采集设计方案

- 2、fpga调用fifo,fifo深度1万多是资源会消耗很多吗,一般调用是调用多大的...

- 3、什么是FIFO缓存队列

- 4、【专辑:fpga引脚分配】FPGA的引脚如何配置?

求一个fpga高速信号采集设计方案

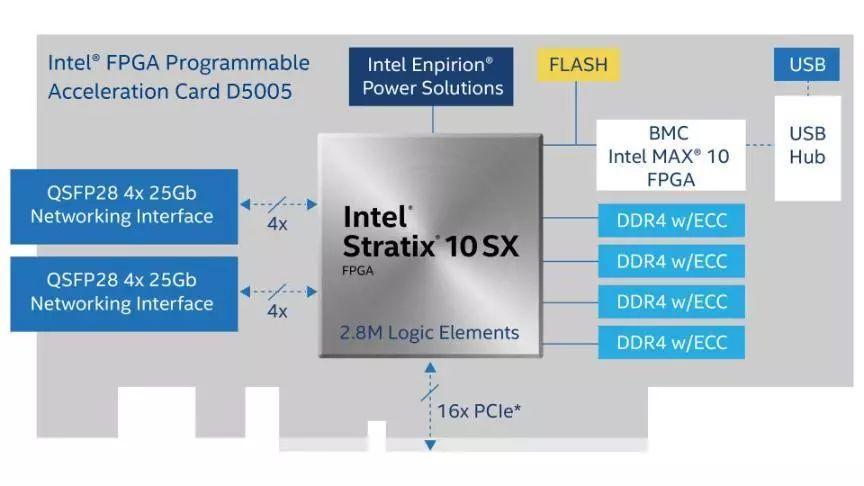

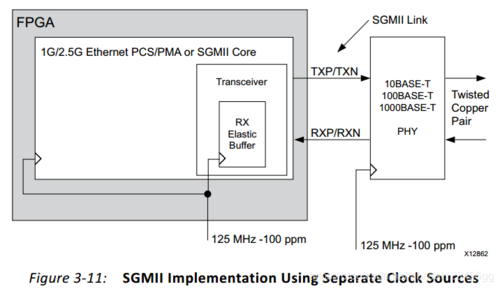

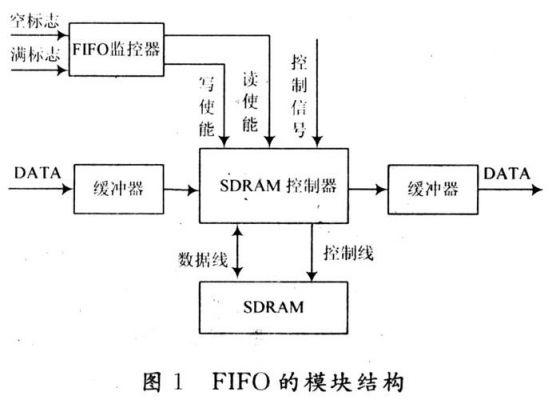

1、IP核控制ADC自动高速转换的状态机。其作用是实现高速100M的信号采样,就是一个循环的时序控制,让ADC转换一次完成之后由FPGA读出数据并将数据交由第二个IP核(FIFO缓存控制IP),然后立刻读取第二次数据。

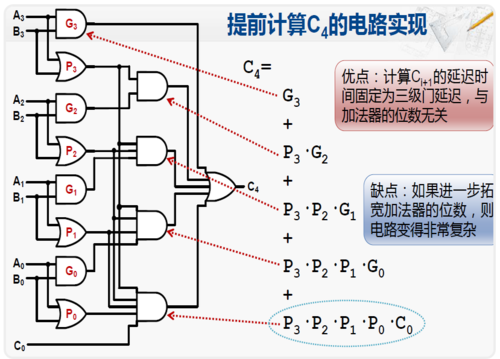

2、流水线(Pipelining)技术在速度优化中相当流行,它能显著提高系统设计的运行速度上限,在现代微、数字信号处理器、MCU、高速数字系统设计中都离不开流水线技术。

3、,DS18B20应该送数字信号给FPGA,所以不用做AD转换了。但是有可能是串行数据(没看18B20的数据手册),可能需要在FPGA内部串并转换,一般温度传感器数据量不是很大,可以考虑存储在FPGA内部的BRAM内。

fpga调用fifo,fifo深度1万多是资源会消耗很多吗,一般调用是调用多大的...

1、如果不带存储单元的,那就是用逻辑单元构建起来的存储器,比较消耗资源,能小则小吧。没有什么一般调用多少。

2、块rom:主要用于查表、buff、fifo等大量数据的存储和交换。比较手册和应用的需求来确定够不够。GCLK:FPGA的时钟设计非常重要,时钟信号不到万不得已一定要走快速时钟线。

3、FIFO是First Input First Output的缩写,先入先出队列,这是一种传统的按序执行方法,先进入的指令先完成并引退,跟着才执行第二条指令。

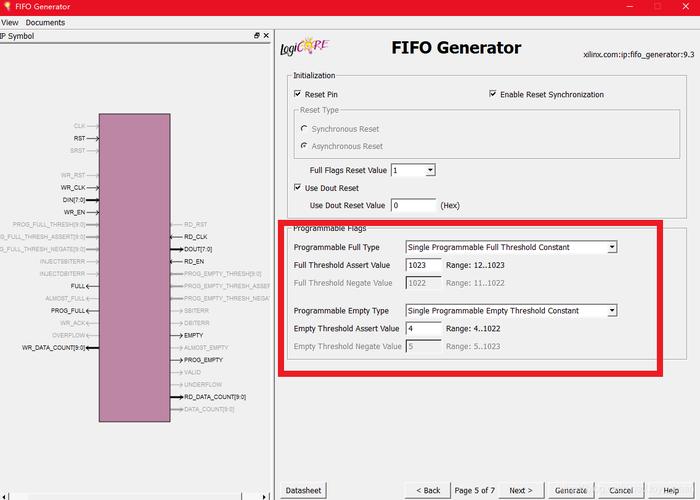

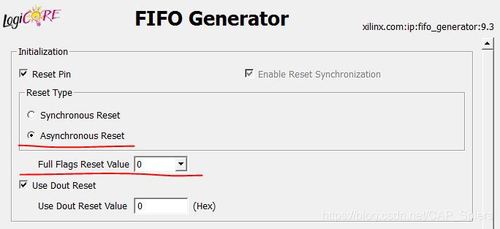

4、储存器,对储存器进行配置。FPGA的储存器配置我们多用ip核来进行配置,当然,IP核可以通过图形界面或者HDL来对参数进行修改以及设置。比如说一个fifo,ram或者rom等储存器。

什么是FIFO缓存队列

FIFO:全称First in, First out,先进先出。LIFO:全称Last in, First out,后进先出。

环形缓冲器 是一种特定的 队列 。所以它也被称作为 圆形队列 。如果你对于队列不太熟悉的话,你从名字上来看你至少能反映出它是一种直线的队伍(如同大家排队去上卫生间)。这个队列里是 先进先出(FIFO) 。

FIFO存储器是一个先入先出的双口缓冲器,即第一个进入其内的数据第一个被移出,其中一个存储器的输入口,另一个口是存储器的输出口。对于单片FIFO来说,主要有两种结构:触发导向结构和零导向传输结构。

队列 又称为先进先出(FIFO—first in first out)线性表。线性表 分为 顺序存储 和 链式存储 ,栈是线性表,所以也有这两种存储方式。同样,队列作为一种特殊的线性表,也同样存在这两种存储方式。

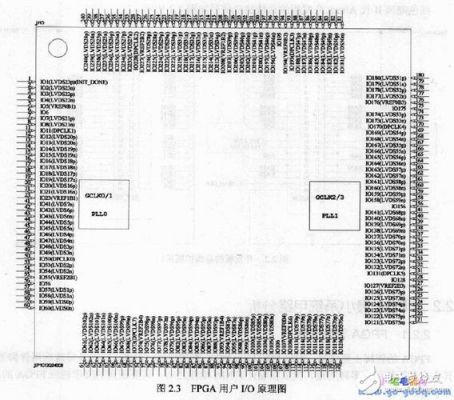

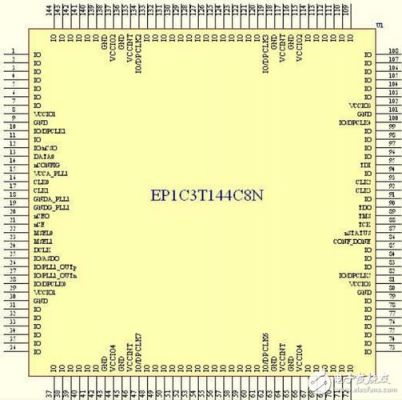

【专辑:fpga引脚分配】FPGA的引脚如何配置?

【FPGA配置模式】FPGA有多种配置模式:并行主模式为一片FPGA加一片EPROM的方式;主从模式可以支持一片PROM编程多片FPGA;串行模式可以采用串行PROM编程FPGA;外设模式可以将FPGA作为微处理器的外设,由微处理器对其编程。

首先,确定数码管的类型。常见的数码管有七段数码管和液晶显示屏。七段数码管用于显示数字,而液晶显示屏可以显示更多的字符和图形。根据数码管的类型,确定需要连接到FPGA芯片的引脚数量。

(1)初始化 系统上电后,如果FPGA满足以下条件:Bank2的I/O输出驱动电压Vcc0_2大于lv;器件内部的供电电压Vccint为2.5v,器件便会自动进行初始化。

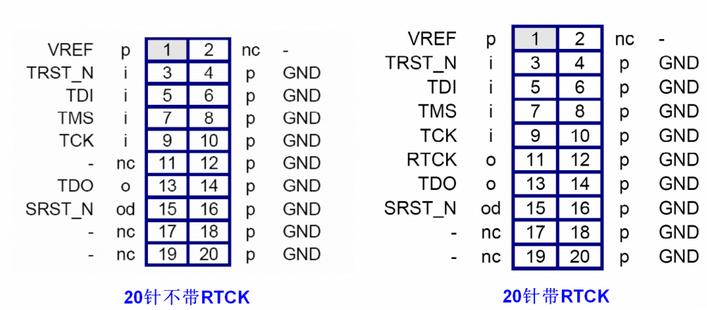

FPGA管脚说明 Altera:用户I/O:不用解释了。配置管脚:MSEL[1:0] 用于选择配置模式,比如AS、PS等。DATA0 FPGA串行数据输入,连接到配置器件的串行数据输出管脚。DCLK FPGA串行时钟输出,为配置器件提供串行时钟。

系统固定的端口比如系统时钟,复位都是固定的,将约束条件复制过来就行,其他自己配置,一般都是板载的扩展IO引脚,这个自己随便配置呀。

在FPGA中,有些管脚不会使用到,为了保护FPGA,需要将未使用的管脚状态配置为三态输入或者弱上拉三态输入。

到此,以上就是小编对于fpga标准接口的问题就介绍到这了,希望介绍的几点解答对大家有用,有任何问题和不懂的,欢迎各位老师在评论区讨论,给我留言。

微信扫一扫打赏

微信扫一扫打赏