本篇目录:

DDR布线要求

常规我们DDR3的布局满足以下基本设计要求即可:考虑BGA可维修性:BGA周边器件5MM禁布,最小3MM。DFM 可靠性:按照相关的工艺要求,布局时器件与器件间满足DFM的间距要求;且考虑元件摆放的美观性。

DDR的地址和控制信号线为一组,和DDR 的CLK的布线长度相差不超过400mil,信号线之间间隔10mil-15mil,宽度一般为5mil。

(6)数据布线,要求:(1)DQS差分布线,相差不能超10mil、以字节为单位。DQS为参考,DQ、DQM误差不能超20mil、避免DQ平行布线,其他参考表二;(7)VREF线宽要20mil 以上,和其他线保持25mil以上的间距。

Add/CMD节点到两片DDR2之差 ±275mil 所有Add/CMD节点到CPU之差 ±390mil MCLK节点到两片DDR2之差 ±10mil 每种长度匹配要求仅限于DDR2的同一个通道之内。通道和通道间任何信号不需长度匹配。

因为其不等长的原因,需要超过1个(事实上是数个,这个数字现在一般是5-8)钟频完成读、写等操作。数据调取给CPU的缓存也是类似等待的周期。由于引脚的并行排布,不需要担心数据的读取先后造成顺序错误。

高级”。实际设计中,为了保证信号有足够的保持时间,或减小同组信号之间的时间偏移,往往不得不故意进行绕线,例如DDR*(DDR1/DDR2/DDR3)中的DQS与DQ信号组要求要严格等长以降低PCB skew,这时就要用到蛇形线。

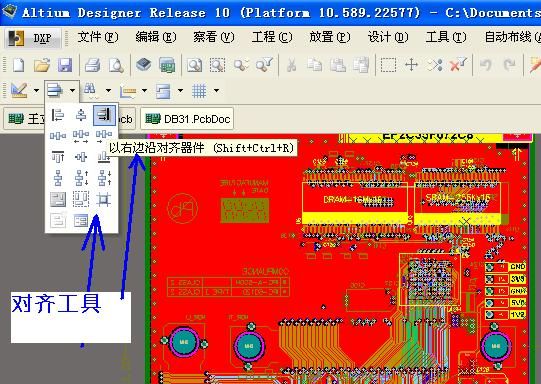

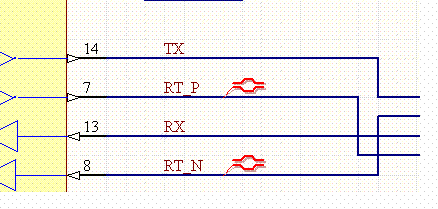

设置差分等长为什么有一个设置不了怎么回事

这个不能设置 ,只能自己调长度,自己调(当然你可以设置他们的误差范围)2 就跟做单根线的等长是一样的,做差分等长的时候 先选择差分走线---选择单根模式--然后做等长就可以了。

因为你需要拉线的那个位置的长度不够拉到4000,另一种可能是你的设置里面有设置最高拉线幅高和幅宽,超出这个值就拉不了。

先确认那两个网络有没有配置为差分信号对Differential Pair。

一般是引出处做一点延长,如果两个引脚是在距离太远,那就只能走蛇形线了 如下图参考。

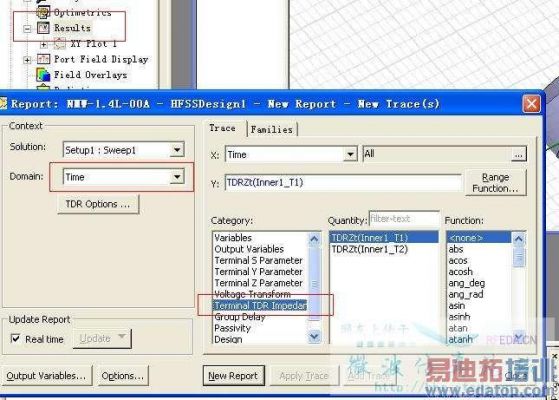

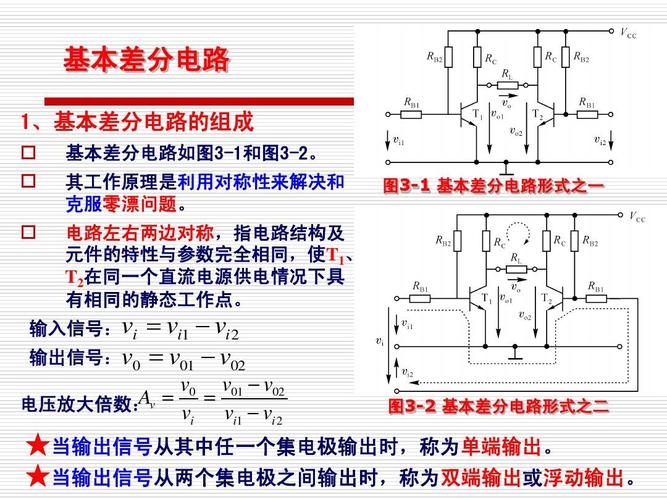

第一个图是Cadence 或者Mentor中的差分对布线为实现多组等长或者阻抗匹配而进行的长度调节后的形状。第二个图是DXP中正常状态的差分对。

差分线不严格等长,怎么办

pcb差分线按以下方法绕等长:连接好需要绕等长的线。T+R开始绕等长,TAB键调出等长属性设置框。

根据有关信息查询是因为设置的差分线的最大或最小间距不合适所致,修改后即恢复正常。两根差分线的长度要尽量一样长,业界一般保证10mil误差以内,严格点的就按5mil以内作为差分线等长要求。

如果差距过大,允许在走线中仅对一根线做蛇形走线以调节长度,但此时等距就没办法了。所以说,差分布线的等长和等距是一对矛盾的要求,差分对布线要求他俩同时成立,实际只能是在两种中做一些妥协,一般优先保证等距。

一般是引出处做一点延长,如果两个引脚是在距离太远,那就只能走蛇形线了 如下图参考。

第一个图是Cadence 或者Mentor中的差分对布线为实现多组等长或者阻抗匹配而进行的长度调节后的形状。第二个图是DXP中正常状态的差分对。

急!懂PCB电路板设计的高手进来,关于差分对等长的问题

一般是引出处做一点延长,如果两个引脚是在距离太远,那就只能走蛇形线了 如下图参考。

我最近也在画这个,如果你这两个差分信号是属于一个组的,就是有关系的话,最好是等长的,这样保证这两个信号的时延是一致的。如果这两个差分信号没关系,那就不需要等长。

不同对要看情况,如果系统设计要求不同对之间具有相同的信号传输延时,那么不同对也要求等长。

第一个图是Cadence 或者Mentor中的差分对布线为实现多组等长或者阻抗匹配而进行的长度调节后的形状。第二个图是DXP中正常状态的差分对。

传输线在FR4板材中的传输时延是170ps/inch。IC的输出、输入信号时序是一定的, 如此我们可以算出接收端可接受的最恶劣情况,也就是不同信号线之间的最长走线长度差。

到此,以上就是小编对于差分线绕等长满足规则的问题就介绍到这了,希望介绍的几点解答对大家有用,有任何问题和不懂的,欢迎各位老师在评论区讨论,给我留言。

微信扫一扫打赏

微信扫一扫打赏